# ANALOG NEURAL NETWORK VLSI IMPLEMENTATIONS

A Dissertation

by

# BERNABÉ LINARES-BARRANCO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

December 1991

Major Subject: Electrical Engineering

# ANALOG NEURAL NETWORK VLSI IMPLEMENTATIONS

### A Dissertation

bу

### BERNABÉ LINARES-BARRANCO

Approved as to style and content by:

Edgar Sánchez-Sinencio

(Chair of Committee)

Ugur Cilingiroglu

(Member)

Bruce M. W. Brunch

Bruce McCormick

(Member)

Jaime Remizez-Angulo

(Member)

J. W. Howze

(Head of Department)

December 1991

### ABSTRACT

Analog Neural Network

VLSI Implementations. (December 1991)

Bernabé Linares-Barranco, B.S., University of Seville;

M.S., University of Seville;

Ph.D., University of Seville

Chair of Advisory Committee: Dr. E. Sánchez-Sinencio

The objective of this dissertation is to demonstrate the viability of using analog circuit design techniques to build neural network systems in hardware. For this we introduce a novel design approach called transconductance-mode (T-mode). It uses transconductance amplifiers and multipliers for gain stages and capacitors to perform integration operations. Using these elements, together with some extra non-linear resistors, many sets of nonlinear differential equations can be implemented in hardware.

The hardware implementation of artificial neural networks can be formulated as a problem of realizing a specific set of nonlinear differential equations. We will show that the proposed T-mode circuit design technique can be used to emulate the differential equations that describe most of the known neural network systems. We will use this technique to build a variety of programmable neural network systems and to implement a learning neural network associative memory with on chip analog dynamic memory.

To my parents Sara and Bernabé

in the second of

### ACKNOWLEDGMENTS

I would like to thank my advisor, his wife and his daughters for treating me as another member of their family. I would also like to thank all my companions in the microelectronics group, all my friends from the International Student Association, all the people from Club España, and all my other friends for making my life during the three years I spent at Texas A&M very enjoyable. I also want to thank the people from the microelectronics group of Seville for their interest and support in my work and for providing the arrangements of making possible my actual job with them. I am also very thankful to my parents and family for their love and moral support. And finally, I also want to thank God for always taking good care of me and maintaining my spirit strong, happy and healthy.

# TABLE OF CONTENTS

11 30

| CHAPTER |                                           | Page |

|---------|-------------------------------------------|------|

| I       | INTRODUCTION AND BACKGROUND 1848          | ` 1  |

|         | A. The General Neural Network Concept     | •    |

|         | B. Inherently Nonlearning Neural Networks | ,    |

|         | 1. Silicon Retina                         | . •  |

|         | 2. Retina for Color Constancy             |      |

|         | 3. Retina for Movement Detection          |      |

|         | 4. Electronic Cochlea                     | 1    |

|         | 5. Binaural Hearing Chip                  | 19   |

|         | 6. Cellular Neural Networks               | 20   |

|         | C. Inherently Learning Neural Networks    | 23   |

|         | 1. Backpropagation                        | 2'   |

|         | a. STM Equations                          | 2    |

|         | b. LTM Equations                          | 2    |

|         | 2. Neocognitron                           | 3    |

|         | a. STM Equations                          | 3    |

|         | b. LTM Equations                          | _    |

|         | 3. Hopfield Network                       |      |

|         | a. STM Equations                          | 3    |

|         | b. LTM Equations                          |      |

|         | 4. Bidirectional Associative Memory (BAM) | _    |

|         | a. STM Equations                          | _    |

|         | b. LTM Equations                          |      |

|         | 5. Adaptive Resonance Theory (ART)        |      |

|         | a. STM Equations                          |      |

|         | b. LTM Equations                          | 4    |

|         | 6. Kohonen Networks                       |      |

| •       | a. STM Equations                          | 4    |

|         | b. LTM Equations                          |      |

|         | D. Conclusions                            |      |

| II      | NEURON MODELS AND THEIR IMPLEMENTATIONS   | 4    |

|         | A. Physiology of the Biological Neuron    |      |

|         | 1. The Na <sup>+</sup> Channels           | . 5  |

.

| CHAPTER                                                   | Page |

|-----------------------------------------------------------|------|

| a. Chemically Gated Channels                              | 50   |

| b. Voltage Gated Na+ Channels                             | 52   |

| 2. The K <sup>+</sup> Channels                            | 53   |

| 3. The Cl <sup>-</sup> Channels                           | 56   |

| B. An Electrical Circuit Model                            | 56   |

| C. FitzHugh-Nagumo Neuron Model and Circuit Implementatio | n 61 |

| 1. Theoretical Model                                      | 61   |

| 2. Circuit Derivation                                     | 63   |

| 3. Circuit Dynamics                                       | 64   |

| 4. Experimental Results                                   | 70   |

| D. Hysteresis Neuron Model and Circuit Implementation     | 71   |

| E. Non-Oscillatory Neurons                                | 78   |

| F. Conclusions                                            | 82   |

| III HOPFIELD TYPE NEURAL NETWORK IMPLEMENTA-              |      |

| TIONS; THE PROGRAMMABLE APPROACH                          | 83   |

| A. Some Reported Examples                                 | 84   |

| 1. Hopfield's Implementation                              | 84   |

| 2. Pulse-Stream Analog/Digital Implementation             | 89   |

| 3. Stochastic Logic Based Digital Implementation          | 91   |

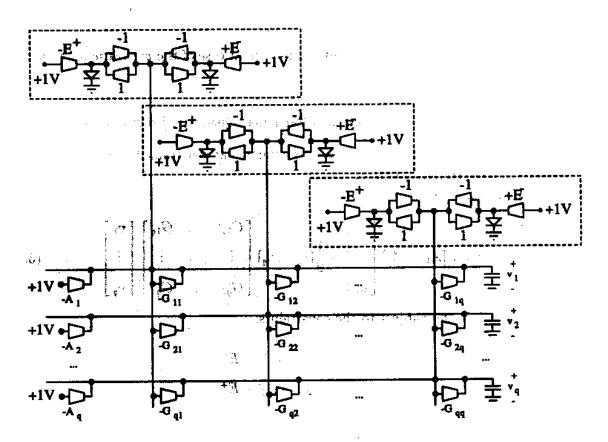

| B. T-Mode Implementation; The Modular Approach            | 94   |

| C. Constraint Optimization Circuits                       | 100  |

| 1. A General Circuit for Constrained Optimization         | 100  |

| 2. T-Mode Implementation of the Quadratic Opti-           |      |

| mization Problem                                          | 103  |

| 3. Hopfield T-Mode Circuit as a Particular Quadratic      |      |

| Programming Circuit                                       | 105  |

| D. Weight Storage                                         | 107  |

| 1. Floating Gate Storage                                  | 108  |

| 2. Capacitor Refreshing Techniques                        | 109  |

| a. Finite Time Memories                                   | 110  |

| b. Stable Memories                                        | 111  |

| E. Oscillatory Type T-Mode Neural Networks                | 112  |

| F. Conclusions                                            | 116  |

| IV BAM NETWORK IMPLEMENTATIONS; THE LEARNING APPROACH     | 117  |

| A. BAM Algorithm Description                              |      |

| A 13 A B A A i b                                          | 119  |

| CHAPTER    |                                                     | Page  |

|------------|-----------------------------------------------------|-------|

|            | 2. BAM Encoding                                     | 123   |

|            | 3. BAM Capacity                                     |       |

|            | 4. Learning in Adaptive BAMs                        |       |

|            | B. A Reported Implementation Example                |       |

|            | C. T-Mode Implementation; The Modular Approach      | 135   |

|            | D. The Learning Circuit                             | 138   |

|            | 1. A Mixed Analog/Digital Learning Circuit for Neu- |       |

|            | ral Networks                                        | 138   |

|            | 2. T-Mode Learning Circuit Implementation           | 140   |

|            | E. Conclusions                                      | . 144 |

| . <b>v</b> | EXPERIMENTAL RESULTS                                | 148   |

|            | A. Programmable Networks                            | 145   |

|            | 1. Programmable BAMs                                | . 146 |

|            | a. Component Characterization                       |       |

|            | b. Associative Memory Implementation Examples       | 162   |

|            | 2. Hopfield Network                                 |       |

|            | 3. Winner-Take-All Network                          | 231   |

|            | 4. Simplified Grossberg Network                     | 236   |

|            | 5. Constrained Quadratic Optimization Circuit       | 252   |

|            | 6. Oscillatory Networks                             | 259   |

|            | a. Oscillatory Hopfield Network                     | 259   |

|            | b. Oscillatory BAM Network                          | 261   |

|            | B. The Learning BAM                                 | . 269 |

|            | 1. The Refreshing Circuit                           | . 276 |

|            | a. Test of Shift Registers                          | . 276 |

|            | b. Test of Refreshing Action                        | . 282 |

|            | c. Test of ADA                                      | . 288 |

|            | d. Test of Complete Refreshing Circuit              | . 293 |

|            | e. A Comment on Spice Simulations                   | . 300 |

|            | 2. The Learning Circuit                             | . 303 |

|            | 3. Associative Memory Implementation Example        | . 308 |

|            | C. Conclusions                                      | . 318 |

| VI         | CONCLUSIONS AND FUTURE WORK                         | . 310 |

|            | REFERENCES                                          | . 318 |

|            | VITA                                                | . 32! |

# LIST OF FIGURES

| FIGURI |                                                                                             | Page |

|--------|---------------------------------------------------------------------------------------------|------|

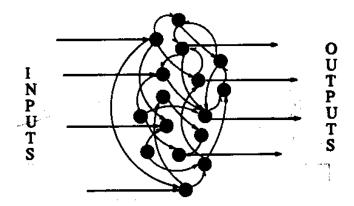

| 1      | General Neural Network Concept                                                              | 3    |

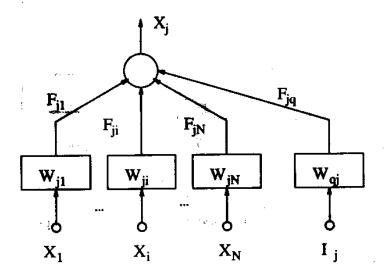

| 2      | General Interconnection Topology for One Neuron                                             | 4    |

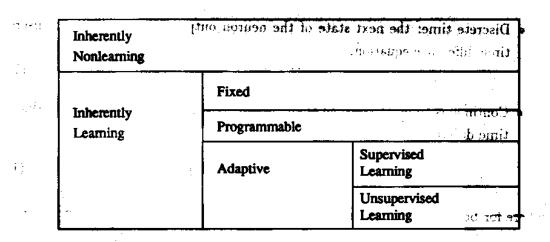

| 3      | Neural Networks Classification                                                              | 6    |

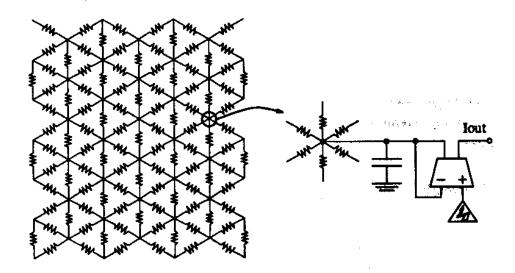

| 4      | Structure of Silicon Retina Chip and Pixel                                                  | 8    |

| 5      | Circuit Schematic of Photoreceptor at Each Pixel                                            | 9    |

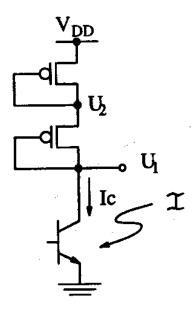

| 6      | Shape of Experimental Relationship between $I_c$ and $U_1$                                  | 10   |

| 7      | Implementation of Double Output Transconductance Amplifier                                  | 10   |

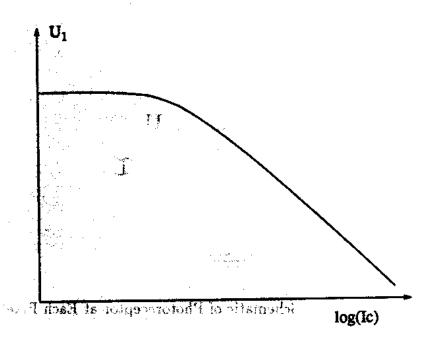

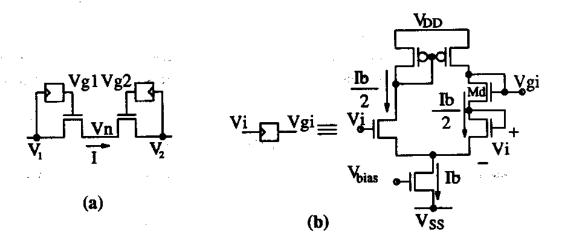

| 8      | (a) Circuit for Resistive Interconnections Implementation; (b) Detail of Bias Circuit       | 11   |

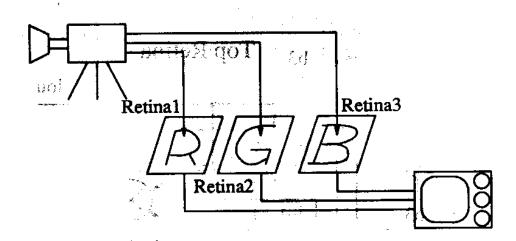

| 9      | Basic Diagram of Color Constancy Retina                                                     | 13   |

| 10     | Retina Diagram with "Edginess" Compensation                                                 | 14   |

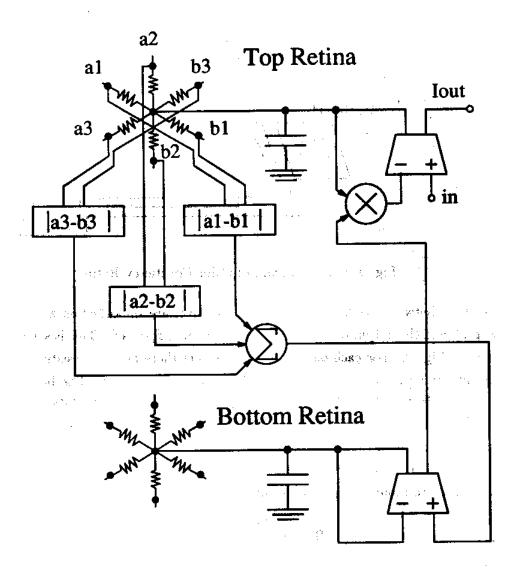

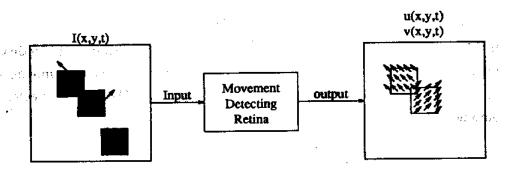

| 11     | Schematic Representation of the Operation of the Movement Detecting Retina                  | 14   |

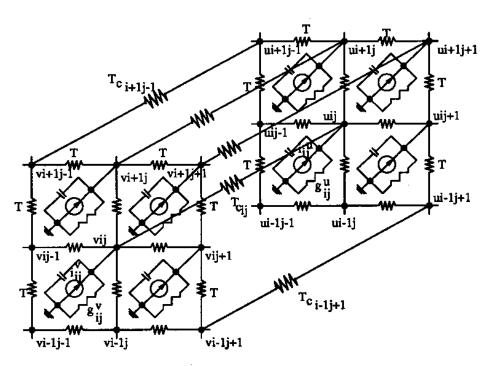

| 12     | Resistive Grids Network That Solves the Difference Equations of the Motion Detecting Retina | 16   |

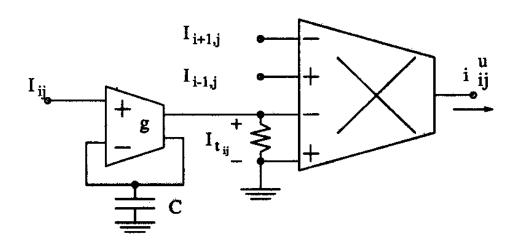

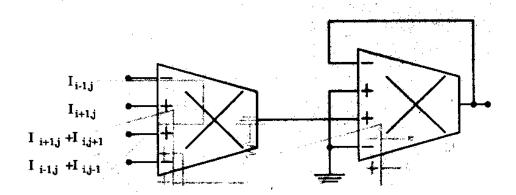

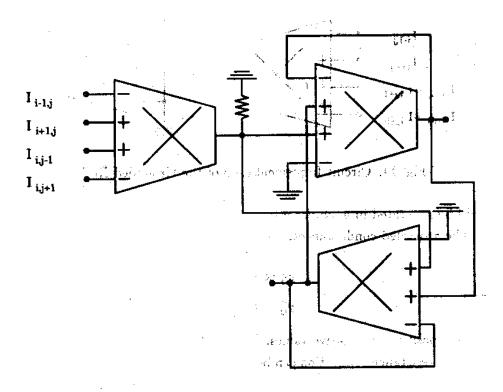

| 13     | Circuit Implementation of $i^u_{ij}$ Current Sources                                        | 16   |

| 14     | Circuit Implementation of the Grounded Resistor $g_{ij}^u$                                  | 17   |

| 15     | Circuit Implementation of the Floating Resistor $T_{c_{ij}}$                                | 18   |

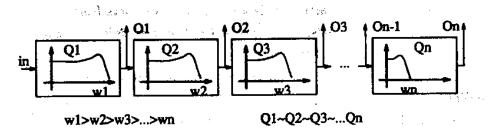

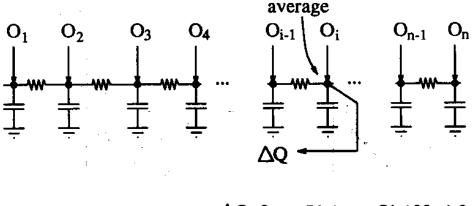

| 16     | Arrangement of Second Order Filters to Simulate the Function of a Cochlea                   | 18   |

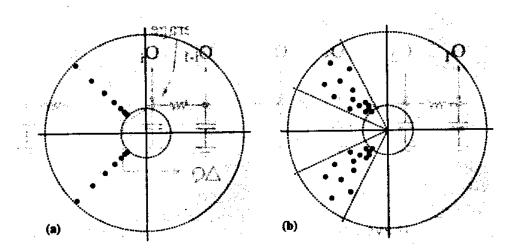

| 17     | (a) Distribution of Poles for an Ideal Cochlea, and (b) for a Practical Implementation      | 19   |

| 18     | Basic Circuit for the Implementation of an AGC in the Electronic Cochlea                    | 20   |

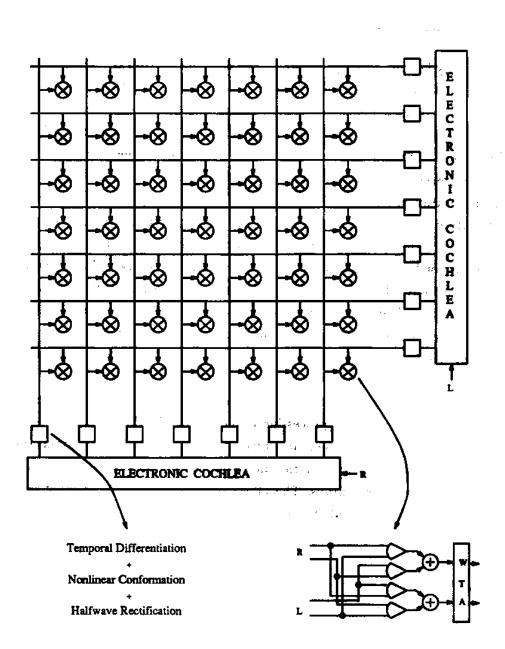

| 19     | Diagram of Binaural Hearing Chip                                                            | 21   |

| 20     | Input-Output Relationship for a Typical Supervised Learning Process                         | 24   |

| FIGURE | E P                                                                                                       | age |

|--------|-----------------------------------------------------------------------------------------------------------|-----|

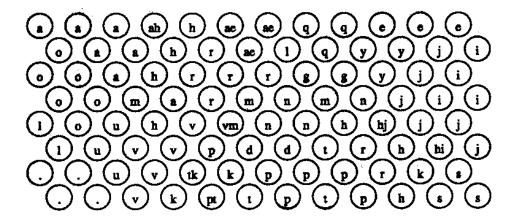

| 21     | Kohonen's Phonetic Self-Organizing Map is a Clear Example of Unsupervised Learning Neural Network Systems | 25  |

| 22     | Schematic Diagram of a Feedforward Short Term Memory                                                      | 26  |

| 23     | Diagram of Backpropagation Neural Network Algorithm Structure or STM                                      | 28  |

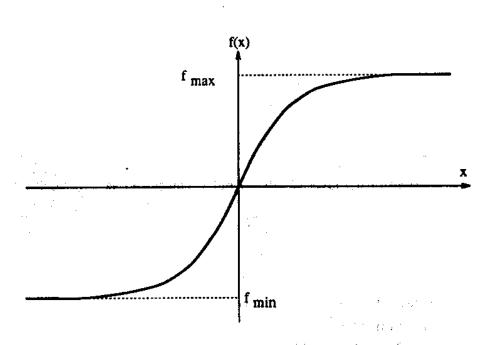

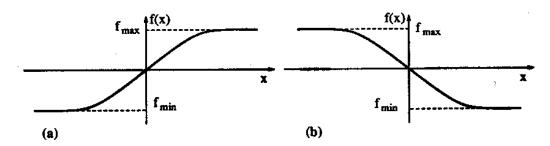

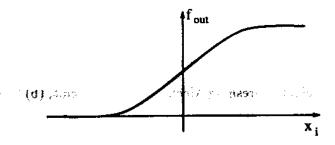

| 24     | Shape of Sigmoidal Function $f(\cdot)$                                                                    | 28  |

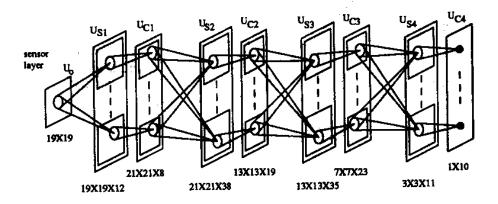

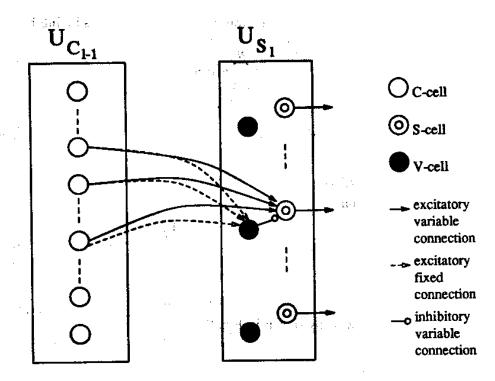

| 25     | Architecture of the Neocognitron for Handwritten Numerals Recognition                                     | 31  |

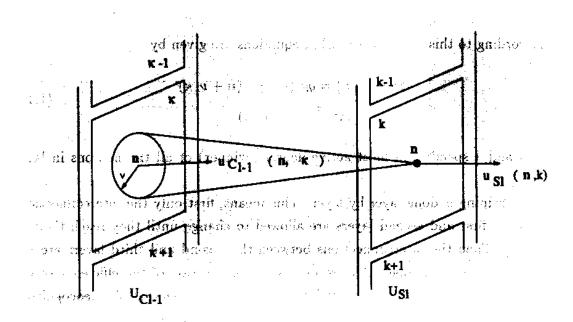

| 26     | Illustration of Interconnections from Neurons in a C-Layer to the Neurons in the Next S-Layer             | 31  |

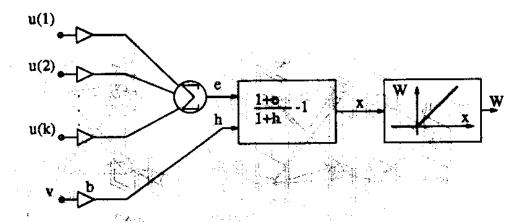

| 27     | Schematic Illustration of Short Term Memory of Neocognitron                                               | 32  |

| 28     | Excitatory Interconnections                                                                               | 33  |

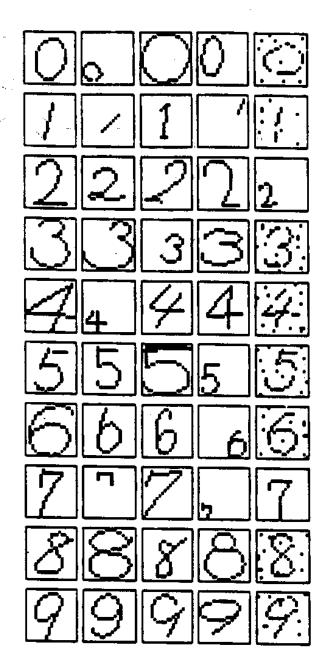

| 29     | Example of Handwritten Numerals Recognized by the Neocognitron Algorithm                                  | 35  |

| 30     | Topology of Hopfield's Neural Network                                                                     | 36  |

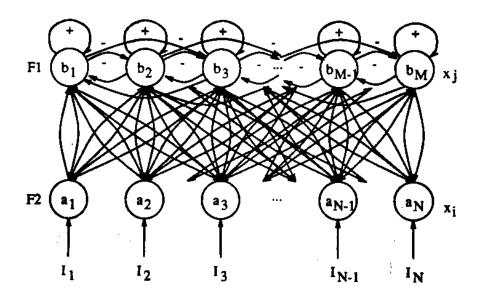

| 31     | Basic Architecture of BAM Algorithm                                                                       | 39  |

| 32     | Simplified Architecture of ART1 Algorithm                                                                 | 40  |

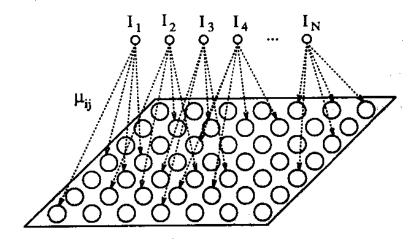

| 33     | Topology of Kohonen's Neural Network                                                                      | 42  |

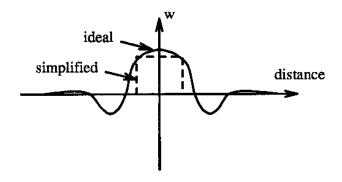

| 34     | Weight Values for the Synapses between Neurons                                                            | 43  |

| 35     | Illustration of the Fact That Active Neurons in the Final Steady State Are within a "Bubble"              | 43  |

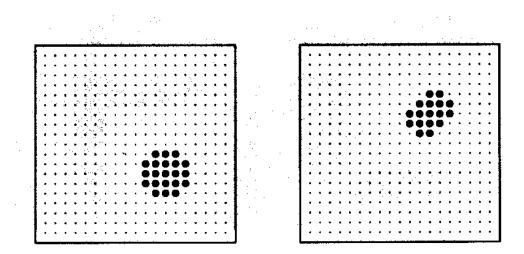

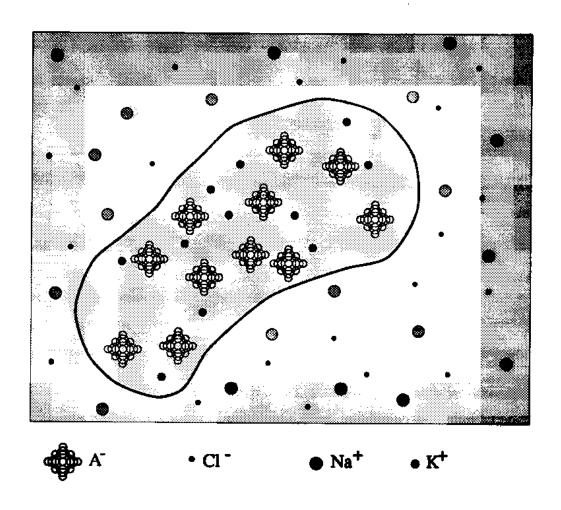

| 36     | Distribution of Electrolytes Inside and Outside a Living Neuron                                           | 47  |

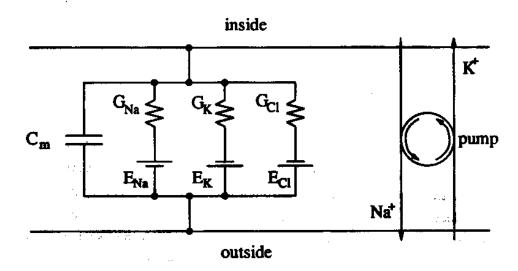

| 37     | Equivalent Electrical Circuit for Electrical Properties of the Nerve Membrane                             | 49  |

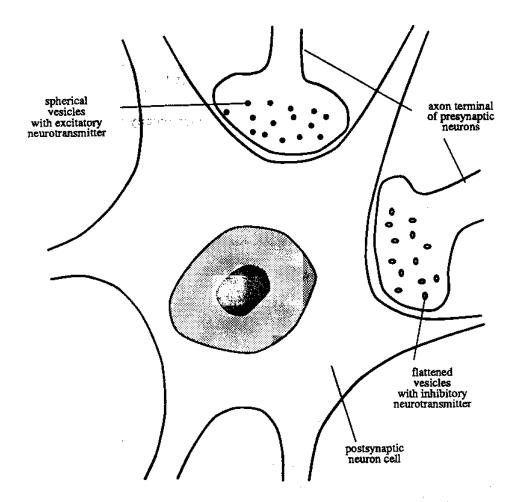

| 38     | Schematic Illustration of Excitatory and Inhibitory Synaptic Connections to a Neuron                      | 51  |

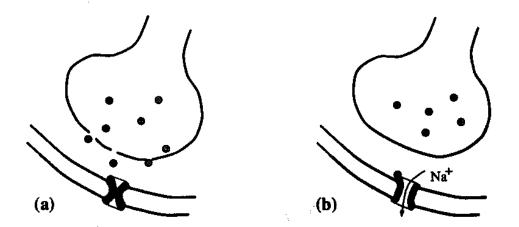

| 39     | Illustration of Opening Mechanism of a Chemically Gated $Na^+$ Channel by an Excitatory Neurotransmitter  | 52  |

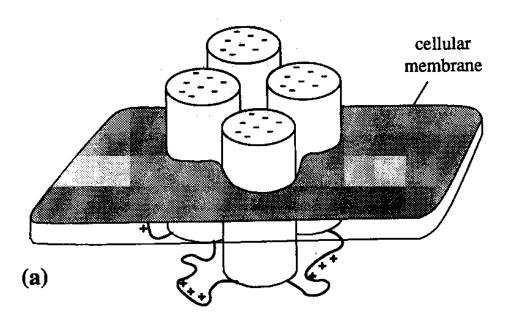

| 40     | Illustration of Structure of a Voltage Gated Na <sup>+</sup> Channel When Closed (a), and When Open (b)   | 54  |

| FIGURE | E Pa                                                                                                                                               | age        |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

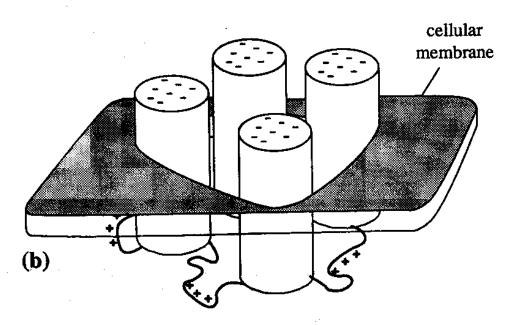

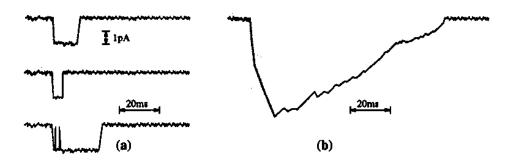

| 41     | <ul><li>(a) Currents through Three Individual Voltage Gated Channels:</li><li>(b) Sum of the Currents through 200 Voltage Gated Channels</li></ul> | 55         |

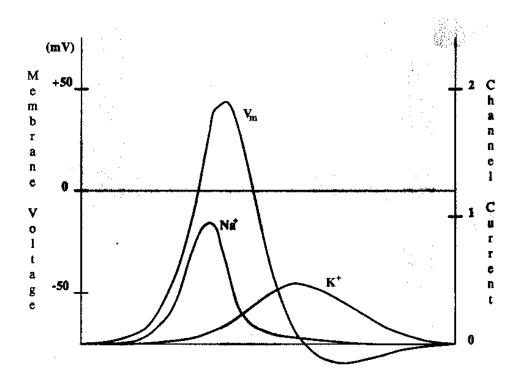

| 42     | Membrane Voltage and Ionic Currents during an Action Potential in a Cell Membrane                                                                  | 55         |

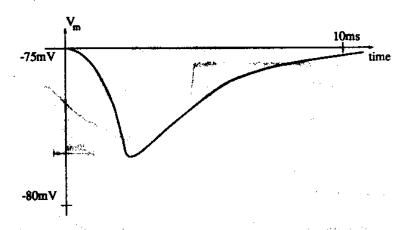

| 43     | Effect of Inhibitory Transmitter, Released by an Inhibitory Synapse, on the Membrane Voltage                                                       | 56         |

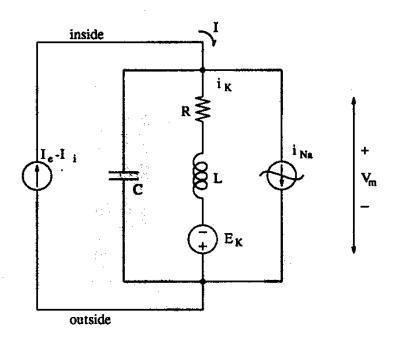

| 44     | Electrical Circuit Model That Explains the Generation of the Action Potential in a Neural Cell                                                     | 57         |

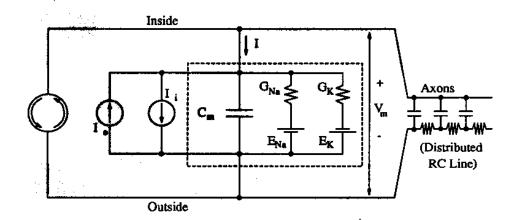

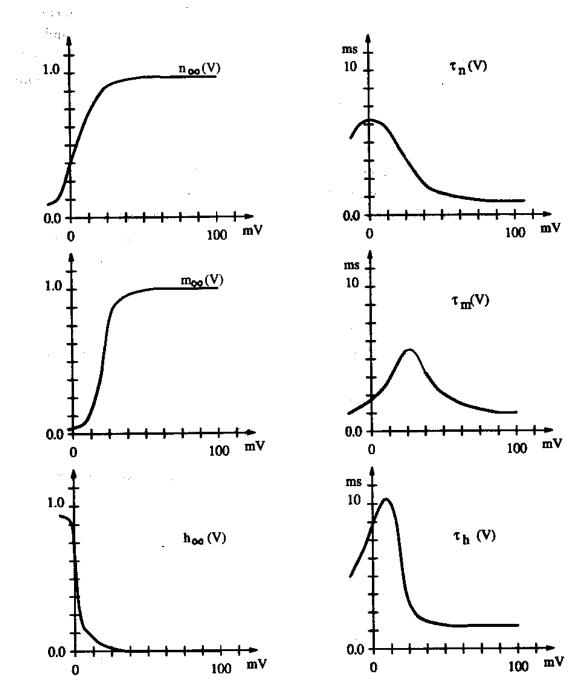

| 45     | Hodgkin-Huxley Curves for Voltage-Only-Dependent Functions of Equations (2.8)                                                                      | 59         |

| 46     | Circuit Diagram for Modeling the Synaptic Connections to One Neuron                                                                                | 61         |

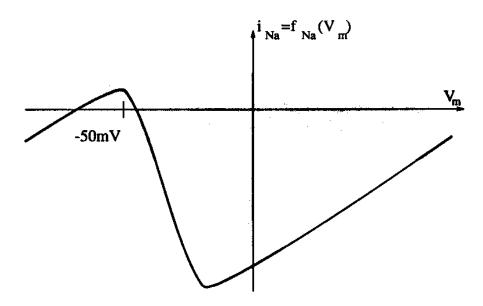

| 47     | Na <sup>+</sup> Current As a Function of Membrane Potential in the Simplified Model Proposed by FitzHugh and Nagumo                                | 62         |

| 48     | Equivalent Circuit for FitzHugh-Nagumo Neuron Model                                                                                                | 62         |

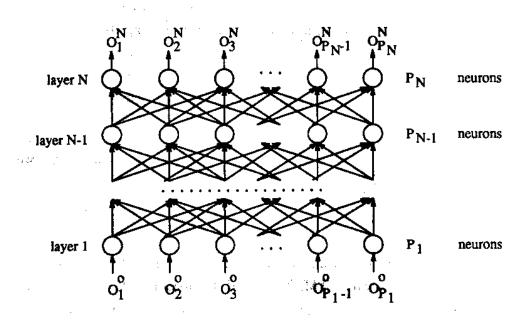

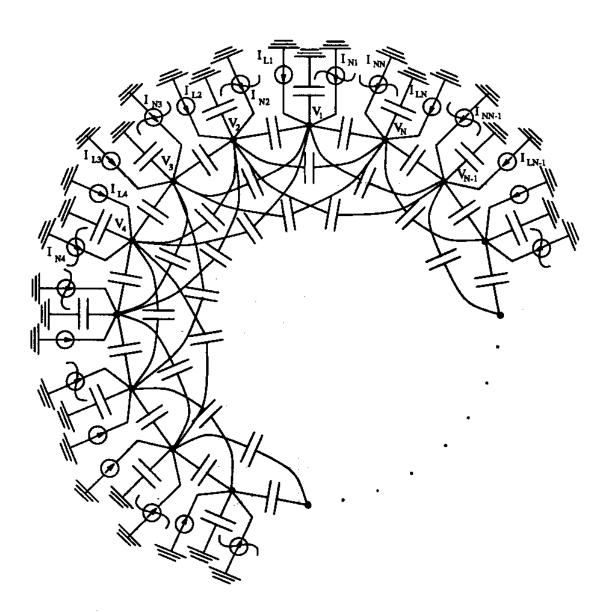

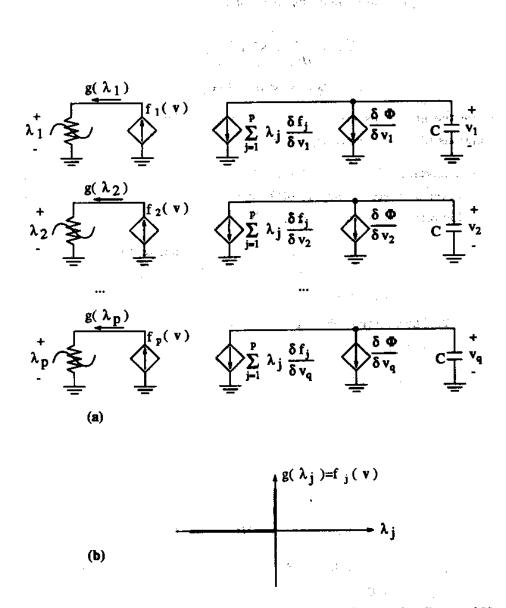

| 49     | General Topology Representing $N$ Nonlinear Differential Equations .                                                                               | 65         |

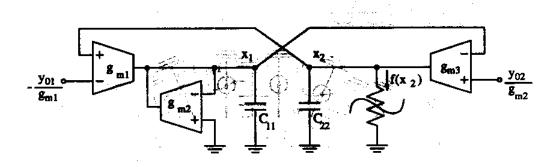

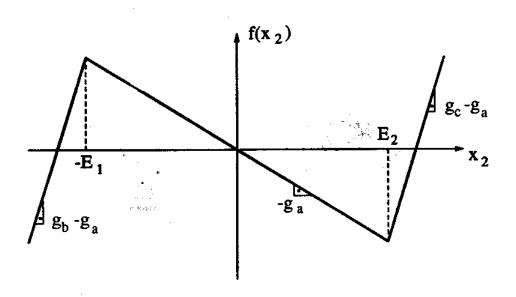

| 50     | T-mode Implementation of FitzHugh-Nagumo's Equations                                                                                               | 66         |

| 51     | N-Shaped Piece Wise Linear Function for Nonlinear Element of Fig. 50                                                                               | 66         |

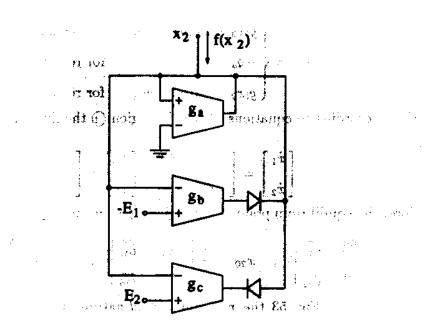

| 52     | Implementation of the Nonlinear Function Using T-Mode Techniques                                                                                   | 67         |

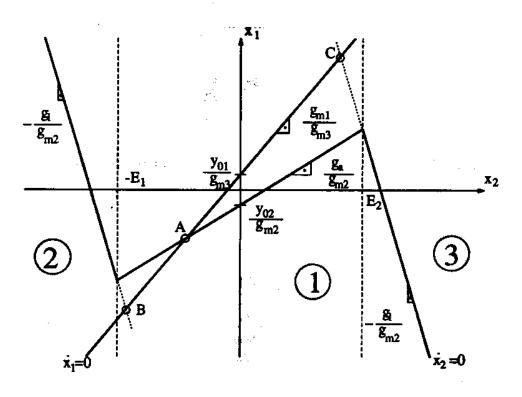

| 53     | Phase Portrait of the System Characterized by Equations (2.18)                                                                                     | 67         |

| 54     | Classification of Equilibrium Points According to the Values of $T_o$ and $\Delta_o$ in Their State Equations                                      | <b>6</b> 9 |

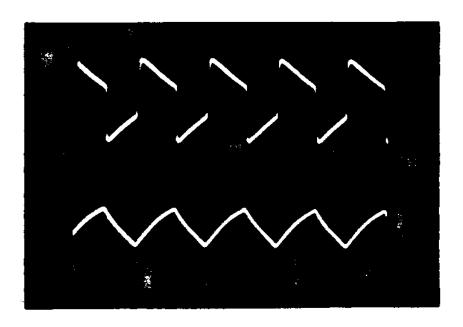

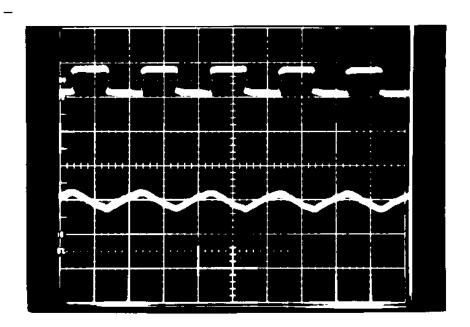

| 55     | Measured Free-Running Oscillations for the Circuit of Fig. 50 When $g_{m1}/C_{11} \ll g_{m2}/C_{22} \ldots \ldots \ldots \ldots$                   | 71         |

| 56     | Input-Output Relation of Oscillator of Fig. 50; Lower Trace Is Input $y_{o2}(y_{o1} = 0)$ , Upper Trace Is Output $x_2 \ldots \ldots \ldots$       | 72         |

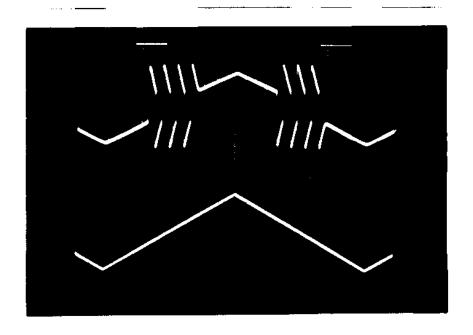

| 57     | Connections of Two Oscillatory Neurons in a Loop                                                                                                   | 72         |

| 58     | Response of a Two-Neuron-Loop Oscillator                                                                                                           | 73         |

| 59     | Hysteresis Transfer Function Extracted from FitzHugh-Nagumo's Model                                                                                | 74         |

| 60     | Equilibrium Points of the Hysteretic System                                                                                                        | 75         |

| 61     | Equilibrium Points of the Modified Hysteretic System                                                                                               | 75         |

| FIGURI | E                                                                                                                                                               | 'age |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 62     | Block Diagram of CMOS Circuit for Modified Hysteretic Neuron Cell                                                                                               | 76   |

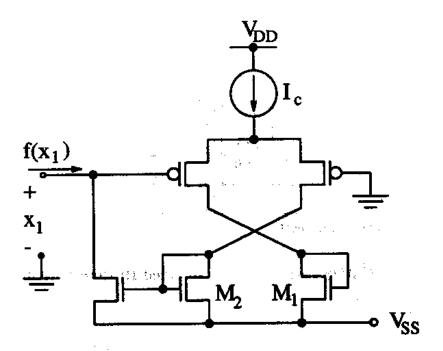

| 63     | CMOS Circuit Implementation for Nonlinear Resistor                                                                                                              | 77   |

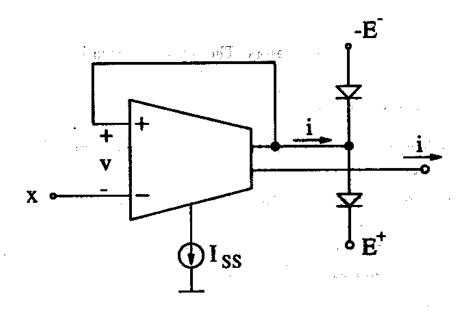

| 64     | Circuit Diagram for T-Mode Hysteresis Amplifier                                                                                                                 | 77   |

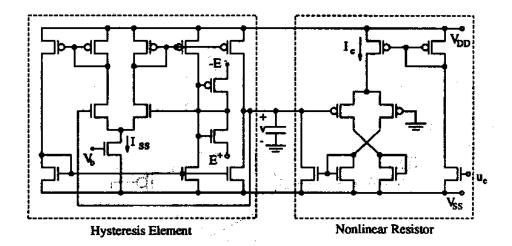

| 65     | CMOS Circuit for the Modified Hysteretic Neuron Cell                                                                                                            | 78   |

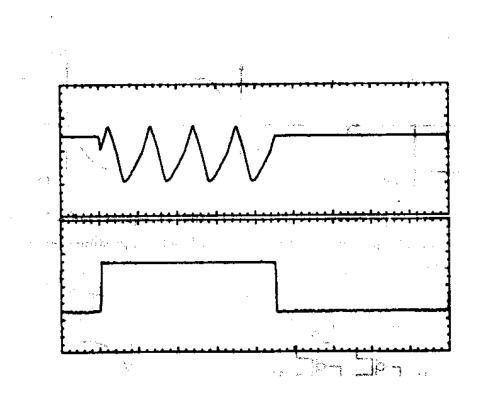

| 66     | Input-Output Relationship for the CMOS Hysteresis Neural Oscillator                                                                                             | 79   |

| 67     | Pattern Generation by a Loop of Two Hysteretic Neural Cells                                                                                                     | 79   |

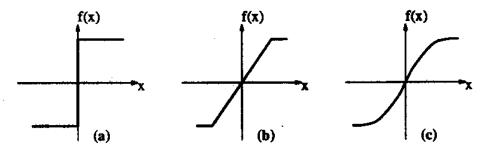

| 68     | Different Dependences between the Output (Frequency) of a Neuron and Its Input; (a) Step Function, (b) Piece-Wise Linear Approximation, (c) Sigmoidal Function  | 80   |

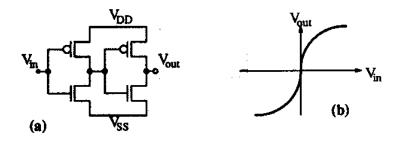

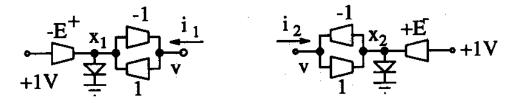

| 69     | (a) CMOS Inverter That Implements the Sigmoidal Voltage Transfer Curve Shown in (b)                                                                             | 80   |

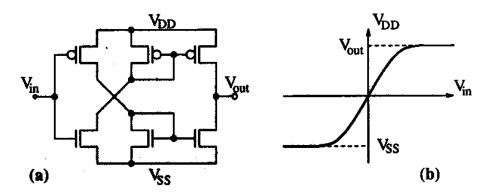

| 70     | (a) CMOS Circuit for Smoothed Sigmoidal Voltage Transfer Function Shown in (b)                                                                                  | 80   |

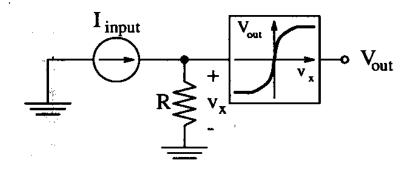

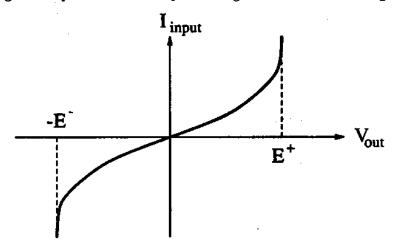

| 71     | Input Current Output Voltage Neuron Circuit Diagram                                                                                                             | 81   |

| 72     | Relation between Variables of Equation (2.36)                                                                                                                   | 81   |

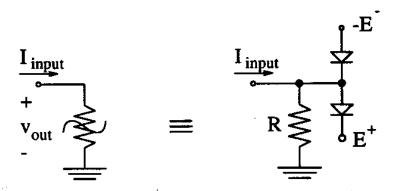

| 73     | Circuit Implementation of Nonlinear Resistor (Current Input Voltage Output Neuron) with Driving Point Characteristics of Fig. 72                                | 82   |

| 74     | Schematic Illustration of Hopfield's Neural Network Algorithm                                                                                                   | 85   |

| 75     | Voltage Amplifier Input-Output Characteristics Used by Hopfield and Tank for Their Hardware Implementation: (a) Noninverting Amplifier, (b) Inverting Amplifier | 87   |

| 76     | Hardware Implementation of Hopfield's Algorithm Proposed by Hopfield and Tank                                                                                   | 88   |

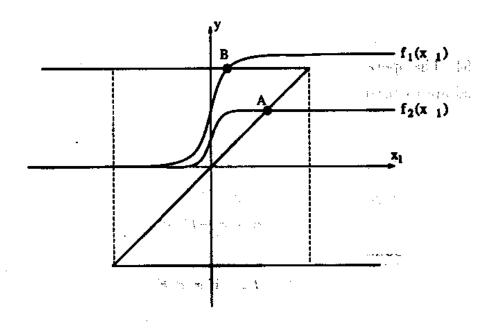

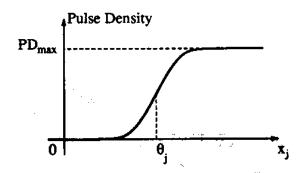

| 77     | Sigmoidal Relationship between Pulse Density of Neuron Output and Value of Non-Pulsing Input Signal                                                             | 89   |

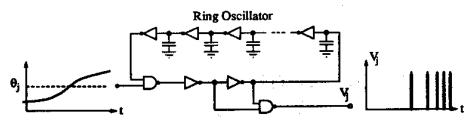

| 78     | Circuit for Pulse Stream Neuron                                                                                                                                 | 89   |

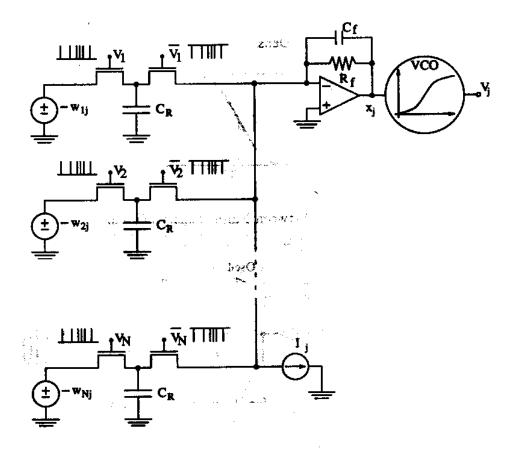

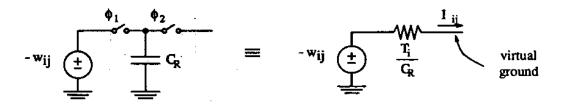

| 79     | Pulse-Stream Synaptic Circuits and Neuron                                                                                                                       | 90   |

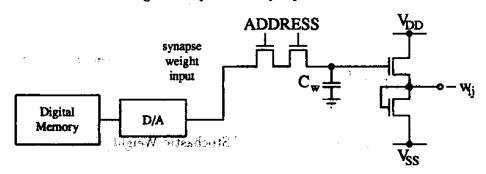

| 80     | Equivalent Synaptic Circuit                                                                                                                                     | 91   |

| 81     | Circuit Implementation of Weight Voltage Sources                                                                                                                | 91   |

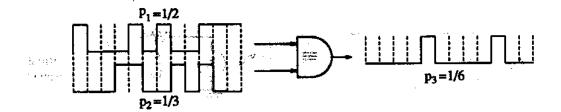

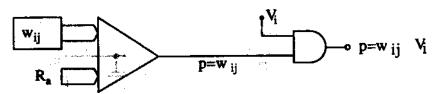

| 82     | Illustration of Stochastic Multiplication                                                                                                                       | 92   |

| FIGURE | E                                                                                                                                   | Page  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------|-------|

| 83     | Generation of Stochastic Weight Signal                                                                                              | 92    |

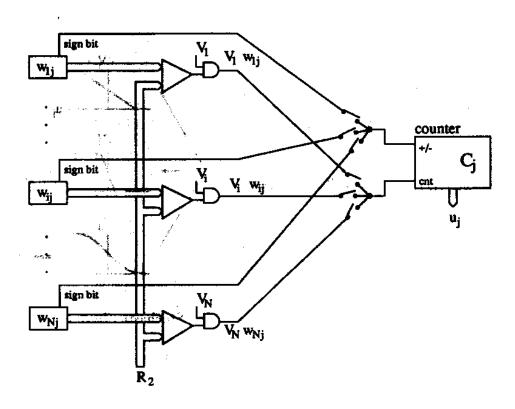

| 84     | Stochastic Logic Circuit for Synaptic Connections to a Single Neuron                                                                | 93    |

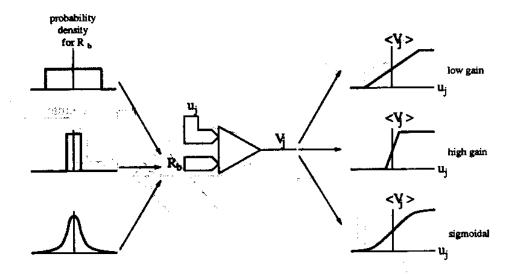

| 85     | Implementation of $f(\cdot)$ Using Stochastic Techniques                                                                            | 94    |

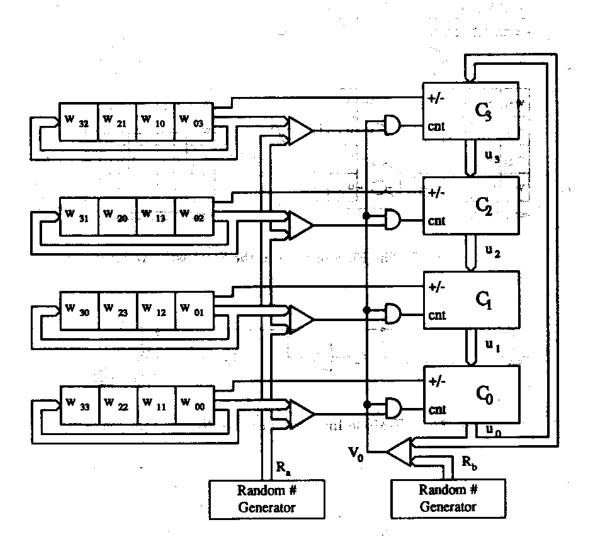

| 86     | The Stochastic Neural Network Architecture                                                                                          | 95    |

| 87     | The Flow of Data in the Stochastic Architecture                                                                                     | 96    |

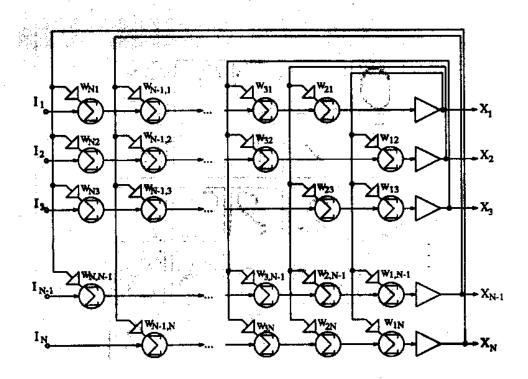

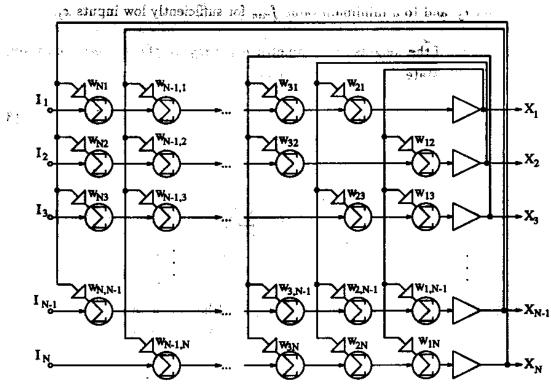

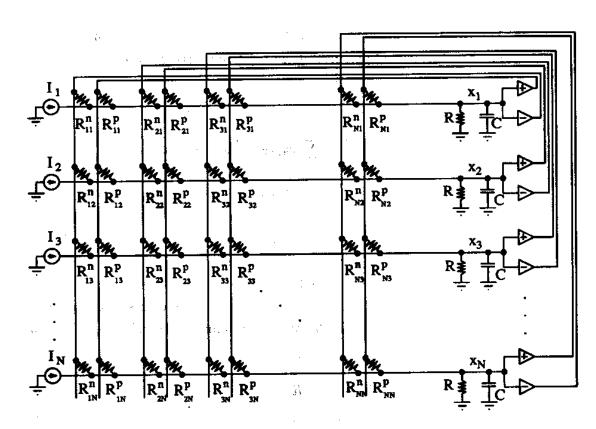

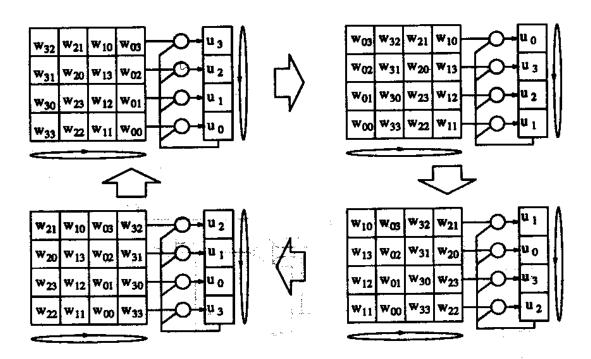

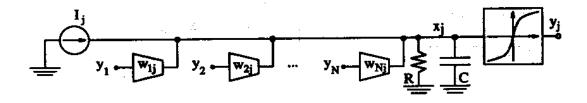

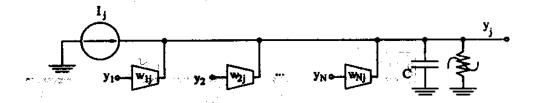

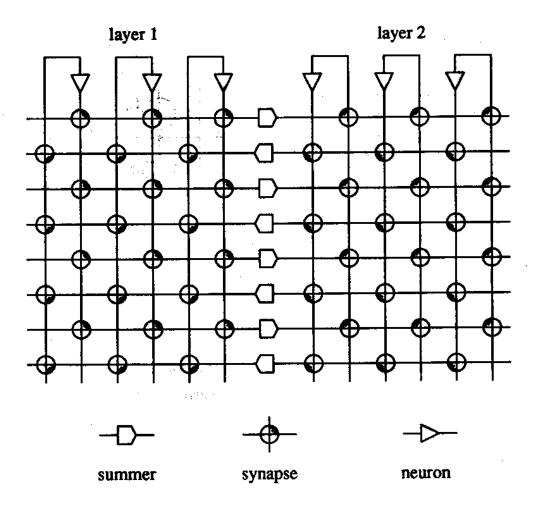

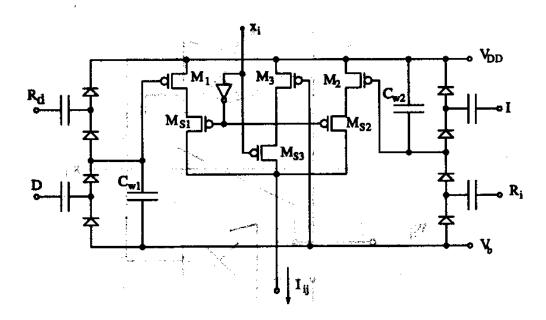

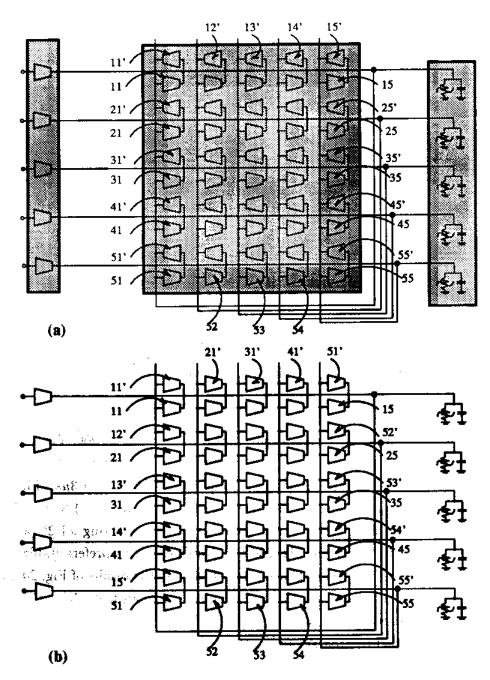

| 88     | A T-Mode Implementation of Neuron Interconnections                                                                                  | 96    |

| 89     | T-Mode Simplified Neuron Implementation                                                                                             | 96    |

| 90     | T-Mode Simplified Implementation of Hopfield Network                                                                                | 97    |

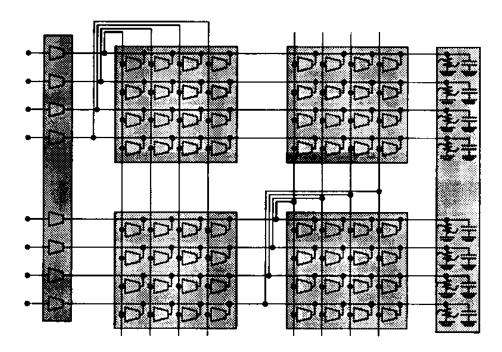

| 91     | Illustration of Modular Capability of the Simplified T-Mode Implementation Technique                                                | 98    |

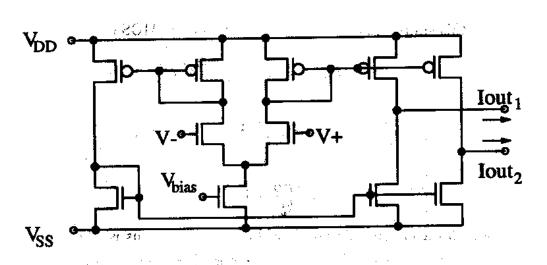

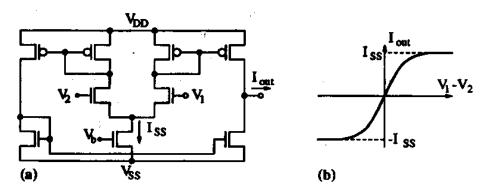

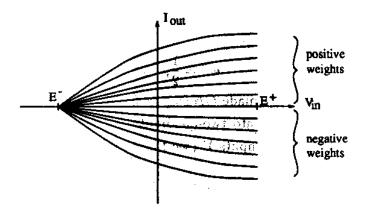

| 92     | (a) Circuit Implementation of Transconductance Amplifier, (b) Transfer Curve                                                        | 98    |

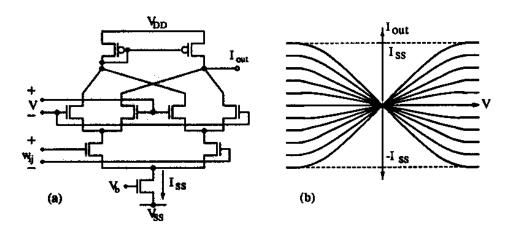

| 93     | (a) Circuit Implementation of Transconductance Multiplier, (b) Transfer Curves $I_{out}$ versus $V$ , for Different $w_{ij}$ Values | 99    |

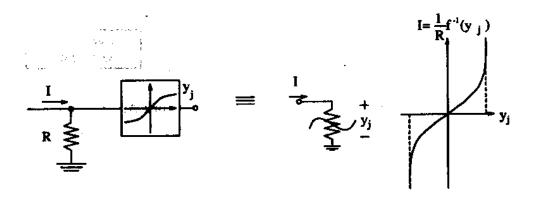

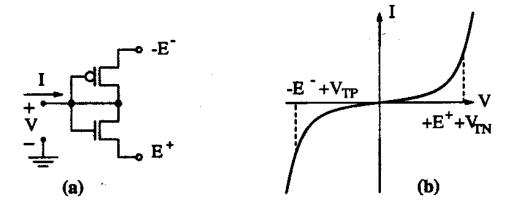

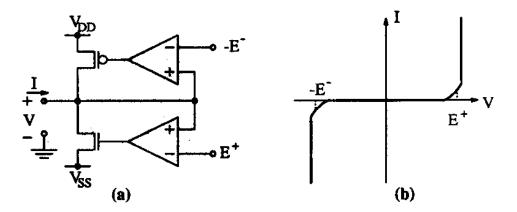

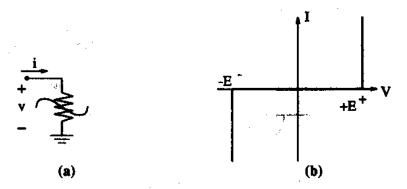

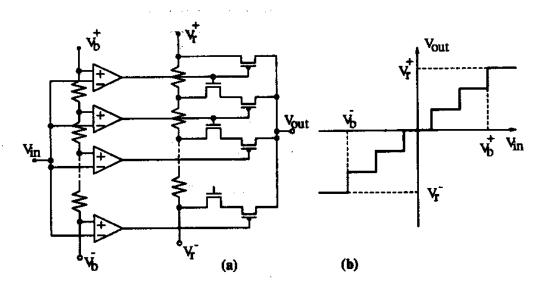

| 94     | (a) Nonlinear Resistor Circuit Implementation, (b) Transfer Curve .                                                                 | 99    |

| 95     | (a) Improved Nonlinear Resistor Implementation, (b) Transfer Curve                                                                  | 99    |

| 96     | (a) General Constrained Optimization Circuit, (b) Transfer Curve of Nonlinear Resistors                                             | 102   |

| 97     | T-Mode Implementation of Constrained Quadratic Optimization  Problem                                                                | 104   |

| 98     | T-Mode Optimization Circuit for Hopfield's Algorithm                                                                                | 106   |

| 99     | Nonlinear Resistors                                                                                                                 | 106   |

| 100    | Nonlinear Resistor Transfer Curve for the Circuit Comprised by Broken Lines in Fig. 98                                              | 107   |

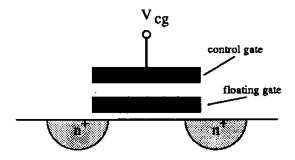

| 101    | Basic Structure of Floating Gate Transistor                                                                                         | 108   |

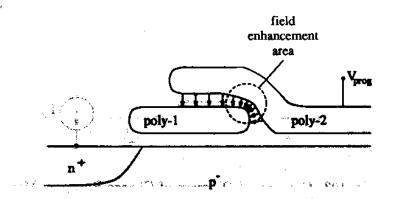

| 102    | Floating Gate Approach for Conventional Double-Poly CMOS Proces                                                                     | s 109 |

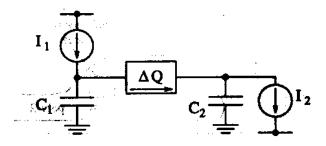

| 103    | Conceptual Diagram of Charge-Pumping Memory                                                                                         | 110   |

| 104    | Switched Capacitor Implementation Example of Charge-Pumping                                                                         |       |

|        | Memory                                                                                                                              | 110   |

| FIGURI | Page                                                                                                                                                                                                                                                           |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

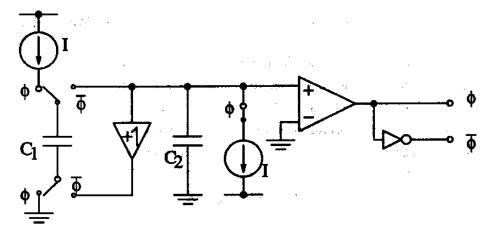

| 105    | Circuit Implementation of Master Slave Memory; (a) Master Circuit, (b) Slave Circuit                                                                                                                                                                           |

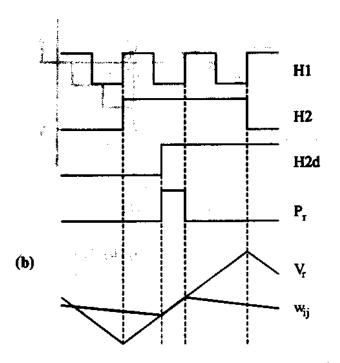

| 106    | Weight Refreshing Mechanism; (a) Circuit, (b) Time Waveforms 113                                                                                                                                                                                               |

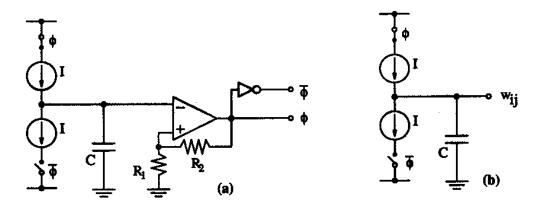

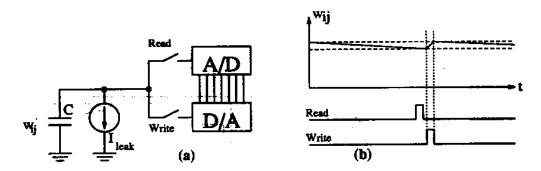

| 107    | Illustration of Refreshing Principle Based on Analog-Digital-Analog  Conversion                                                                                                                                                                                |

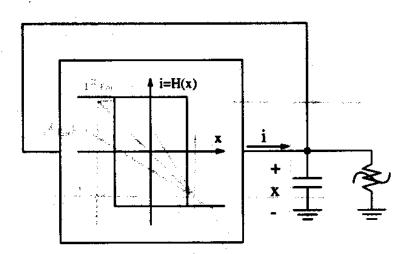

| 108    | (a) Actual ADA Implementation, (b) Transfer Curve                                                                                                                                                                                                              |

| 109    | Relation between the Output Frequency and the Input Voltage of an Oscillatory Neuron                                                                                                                                                                           |

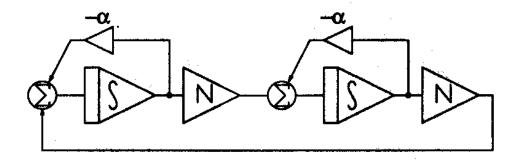

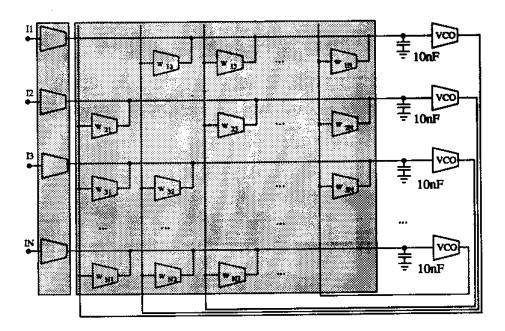

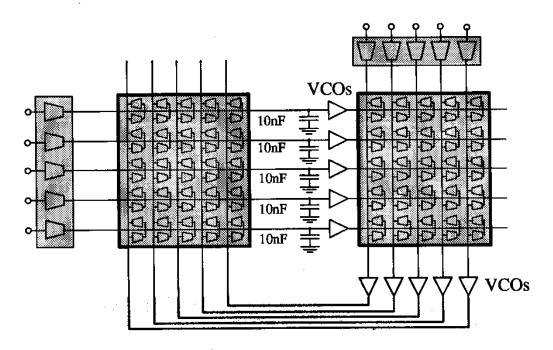

| 110    | T-Mode Implementation of Hopfield Network with Oscillatory Neurons 115                                                                                                                                                                                         |

| 111    | Architecture of BAM Algorithm                                                                                                                                                                                                                                  |

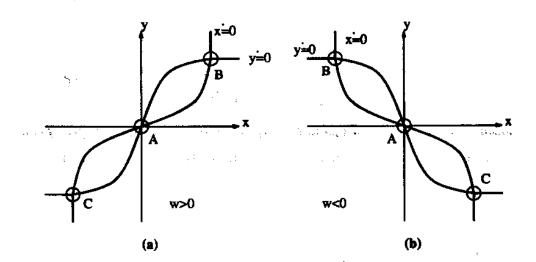

| 112    | Phase Portrait of the $1 \times 1$ BAM: (a) $w > 0$ , (b) $w < 0 \dots 121$                                                                                                                                                                                    |

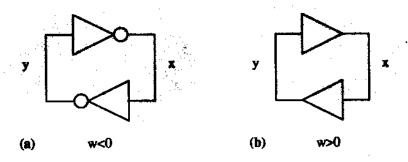

| 113    | The $1 \times 1$ BAM is Equivalent to a 1-Bit Flip-Flop with (a) Inverting Amplifiers if $w < 0$ , and with (b) Noninverting Amplifiers if $w > 0 \dots \dots$ |

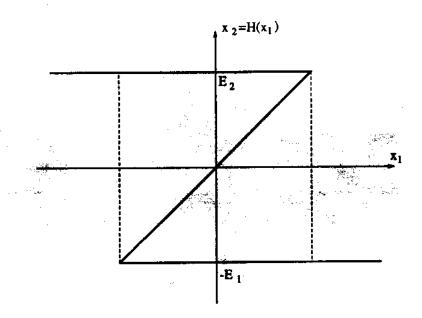

| 114    |                                                                                                                                                                                                                                                                |

| 114    | •                                                                                                                                                                                                                                                              |

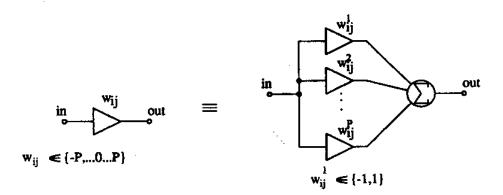

| 115    | Transformation of a Synapse with Discrete Analog Weight into a Set of Parallel Synapses with Digital Weights                                                                                                                                                   |

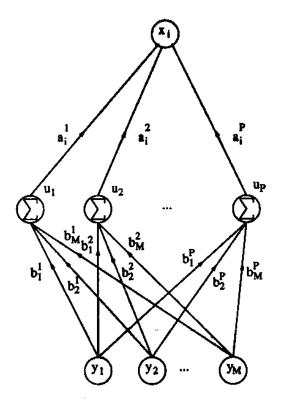

| 116    | Modified Synaptic Interconnections from All Neurons in Layer 2 to One Neuron in Layer 1                                                                                                                                                                        |

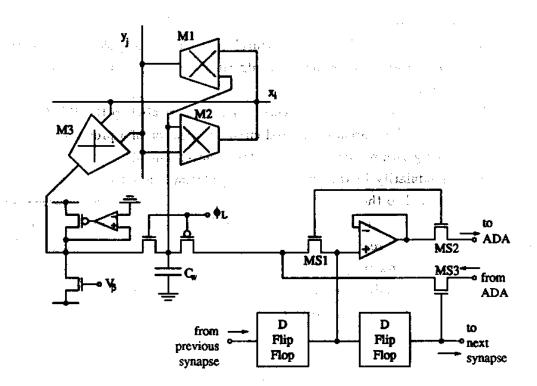

| 117    | Synapse Circuit; The Part Comprised by Broken Lines Only Needs to Be Implemented Once per Neuron                                                                                                                                                               |

| 118    | Circuit Implementation of Summing Circuits and the Following<br>Synaptic Connection; The Part Comprised by Broken Lines Only<br>Needs to Be Implemented Once per Summing Circuit                                                                               |

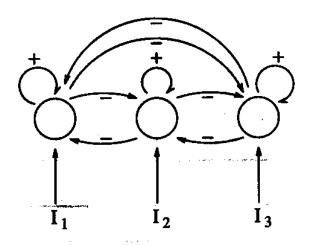

| 119    | Circuit Representation of 3 × 3 BAM                                                                                                                                                                                                                            |

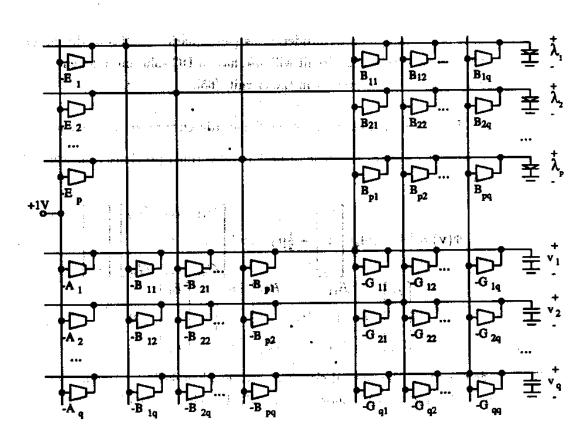

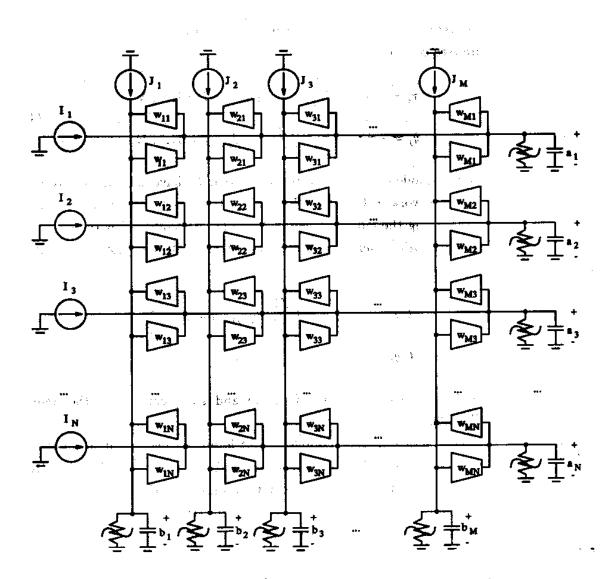

| 120    | T-Mode Circuit Implementation of BAM Algorithm                                                                                                                                                                                                                 |

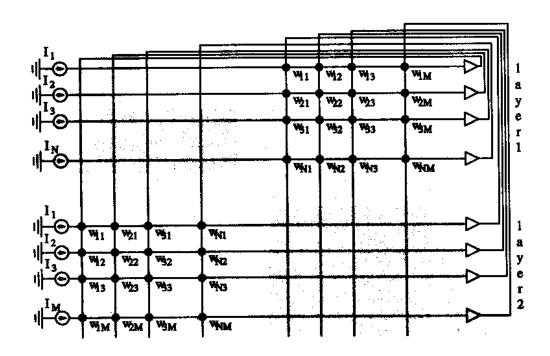

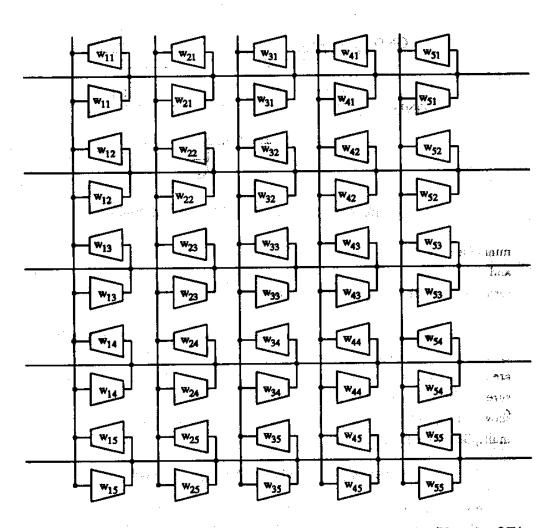

| 121    | Illustration of Modular Capability of T-Mode Circuit BAM Implementation                                                                                                                                                                                        |

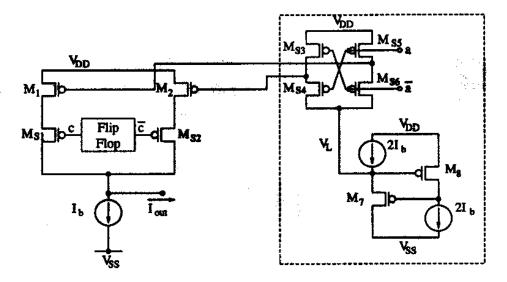

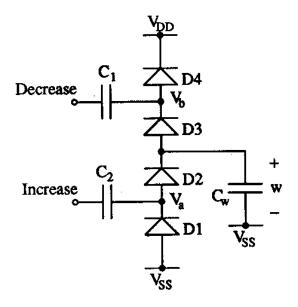

| 122    | Charge Pumping Circuit for Weight Modification                                                                                                                                                                                                                 |

| 123    | Synaptic Circuitry                                                                                                                                                                                                                                             |

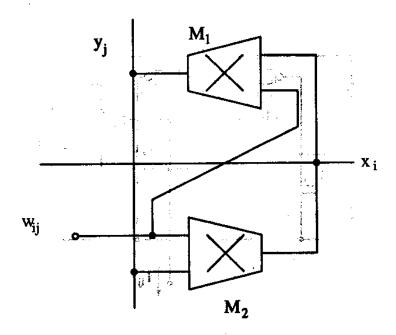

| 124    | Bidirectional Synapse of T-Mode BAM                                                                                                                                                                                                                            |

| FIGURE |                                                                                                          | Page |

|--------|----------------------------------------------------------------------------------------------------------|------|

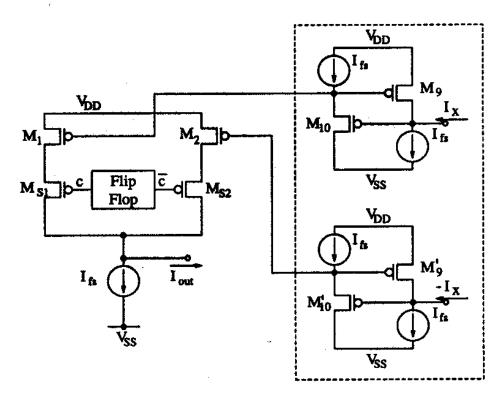

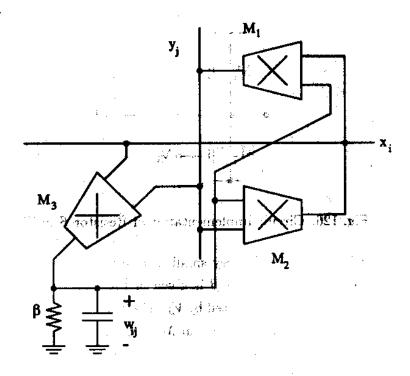

| 125    | Learning BAM Bidirectional Synaptic T-Mode Circuit                                                       | 141  |

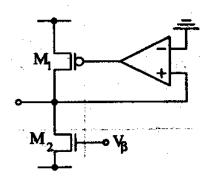

| 126    | Circuit Implementation of Resistor $\beta$ in Fig. 125                                                   | 142  |

| 127    | Complete Synaptic Circuit for T-Mode BAM                                                                 | 143  |

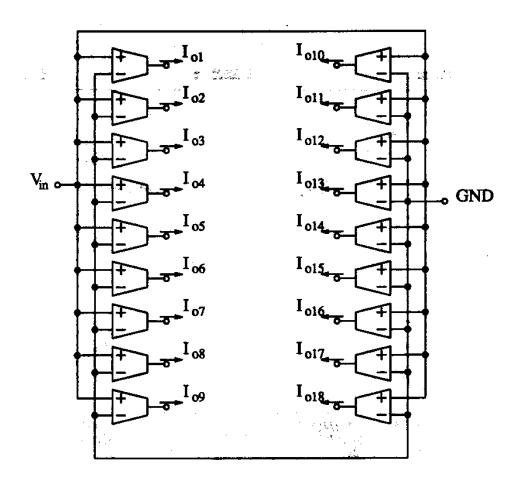

| 128    | Circuit Diagram of Positive/Negative Current Source                                                      | 147  |

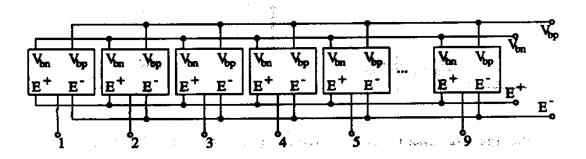

| 129    | Configuration of Input Current Sources Chip                                                              | 149  |

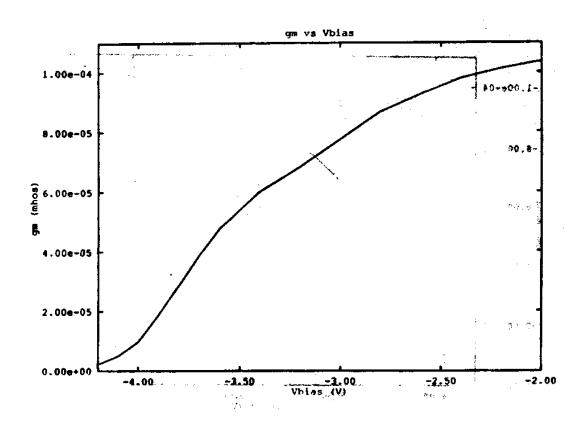

| 130    | DC Transfer Curves of Positive/Negative OTAs for Different $V_{bias}$ Voltages                           | 150  |

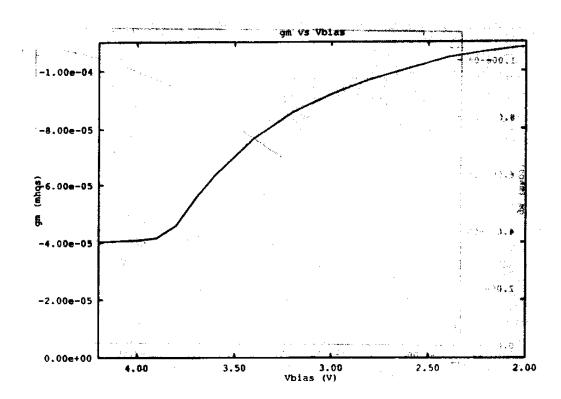

| 131    | Dependence of $g_m$ of Positive/Negative OTAs with Negative Bias Voltages                                | 151  |

| 132    | Dependence of $g_m$ of Positive/Negative OTAs with Positive Bias Voltages                                | 152  |

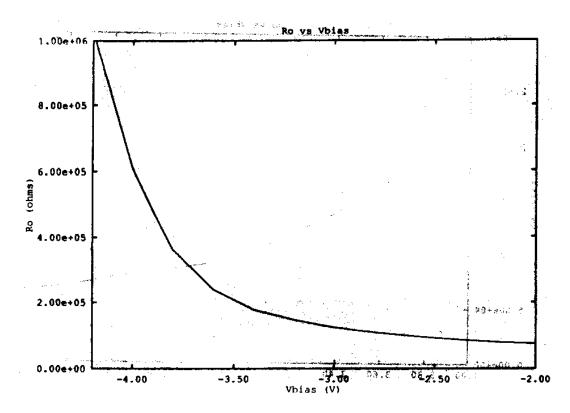

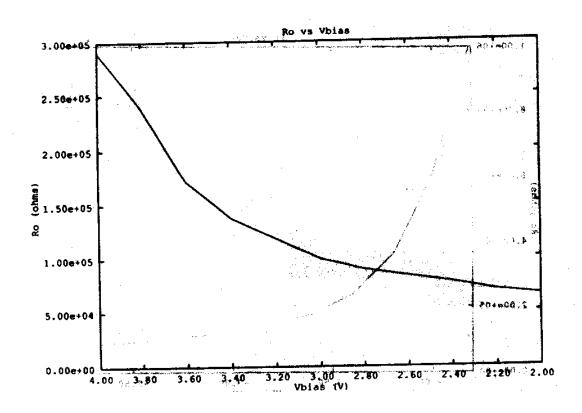

| 133    | Output Impedance of Positive/Negative OTAs for Negative Bias Voltages                                    | 153  |

| 134    | Output Impedance of Positive/Negative OTAs for Positive Bias Voltages                                    | 154  |

| 135    | Complete Circuit Diagram of Fabricated Nonlinear Resistors                                               | 155  |

| 136    | Configuration of Nonlinear Resistor Chip                                                                 | 155  |

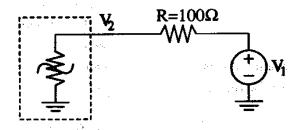

| 137    | Set Up Used for Nonlinear Resistors DC Characterization                                                  | 155  |

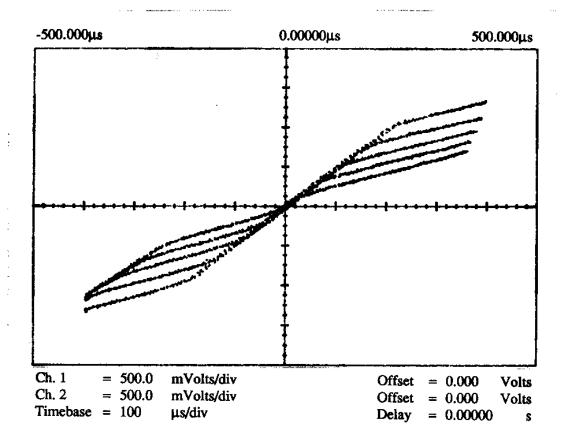

| 138    | Measured $V_2$ versus $V_1$ Transfer Curves for Different Values of $E^+$ and $E^-$                      | 156  |

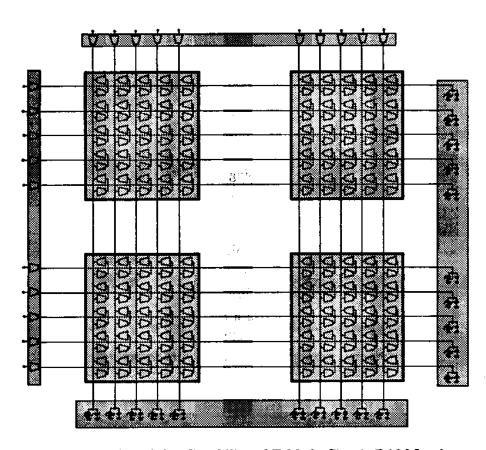

| 139    | Chip Floor Plan of Synaptic BAM Matrix Using Positive/Negative OTAs                                      | 159  |

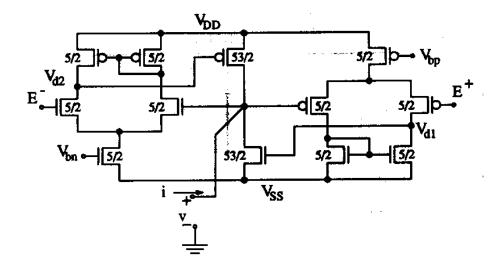

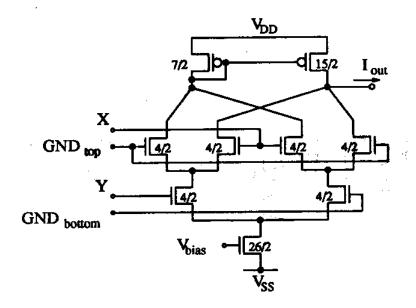

| 140    | Actual Schematic of Fabricated Multipliers                                                               | 160  |

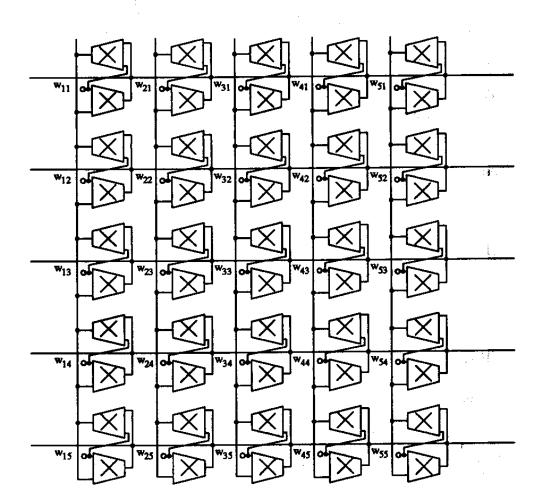

| 141    | Floor Plan of Fabricated BAM Synaptic Matrix with Multipliers                                            | 161  |

| 142    | Experimental Set Up for Measurement of DC Characteristics of the Parallel Connection of Five Multipliers | 162  |

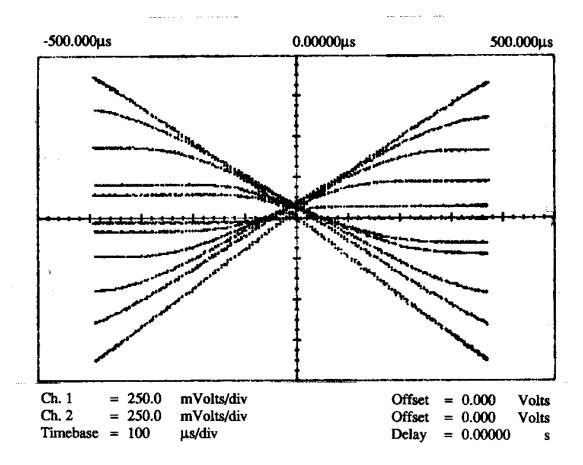

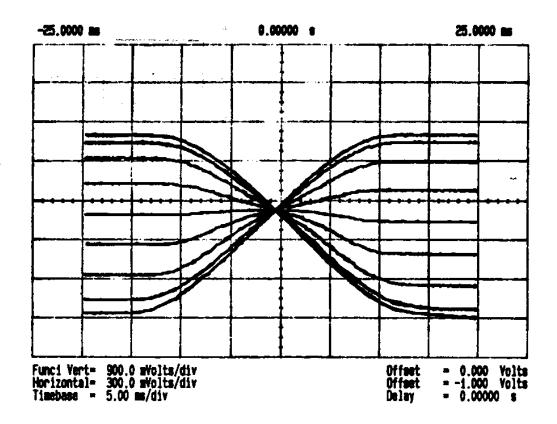

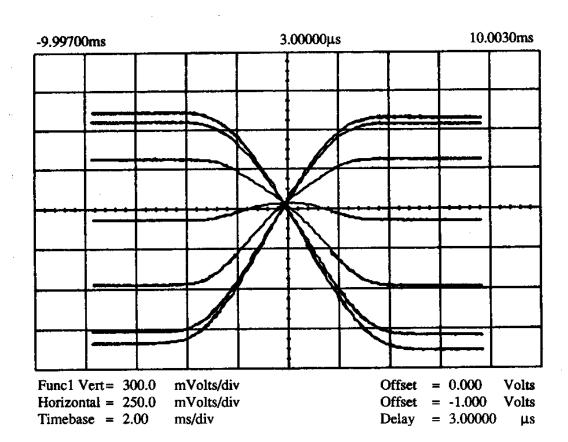

| 143    | Measurement of the DC Transfer Curves of Five Multipliers in Parallel for $V_{bias} = -3.77V$            | 163  |

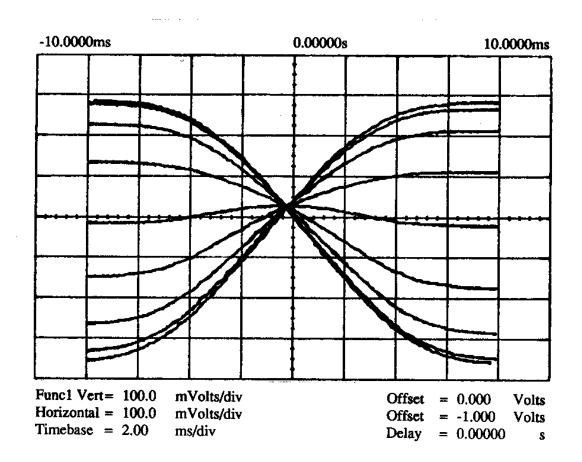

| 144    | Measurement of the DC Transfer Curves of Five Multipliers in Parallel for $V_{bias} = -3.89V$            | 164  |

| FIGURE | E                                                                                                                                                         | Page  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 145    | Measurement of the DC Transfer Curves of Five Multipliers in Parallel for $V_{bias} = -4.00V$                                                             | 165   |

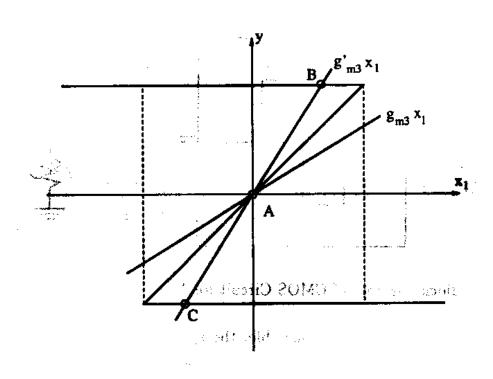

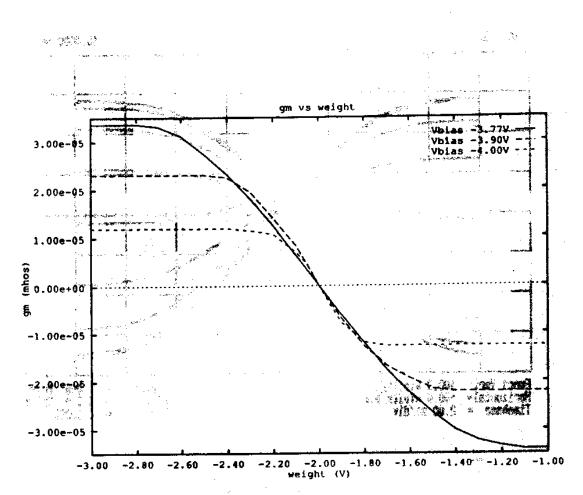

| 146    | Transconductance $g_m$ of One Multiplier versus Weight $w$ for Three Different $V_{bias}$ Voltages                                                        | 166   |

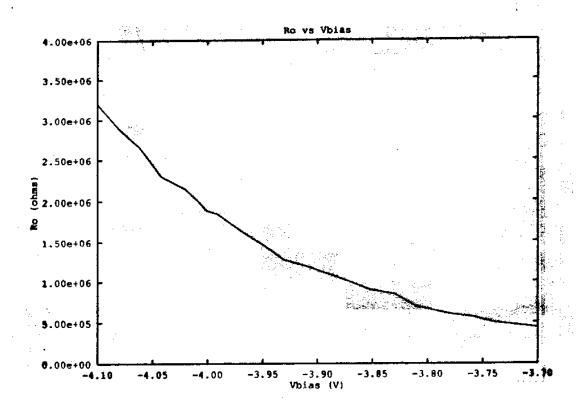

| 147    | Output Impedance of One Multiplier As a Function of $V_{bias}$                                                                                            | 167   |

| 148    | Experimental Set Up for Measuring the Transient Responses in a $5 \times 5$ BAM                                                                           | . 168 |

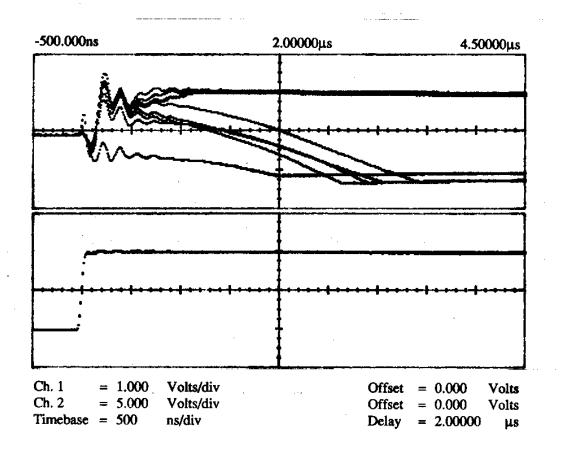

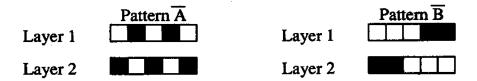

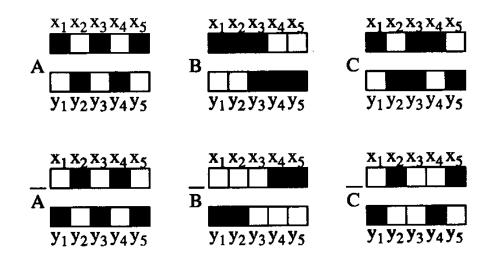

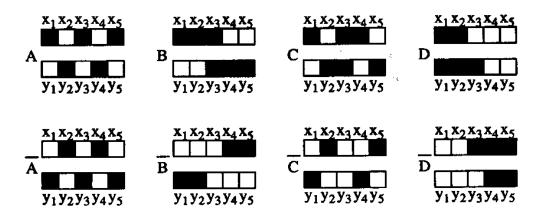

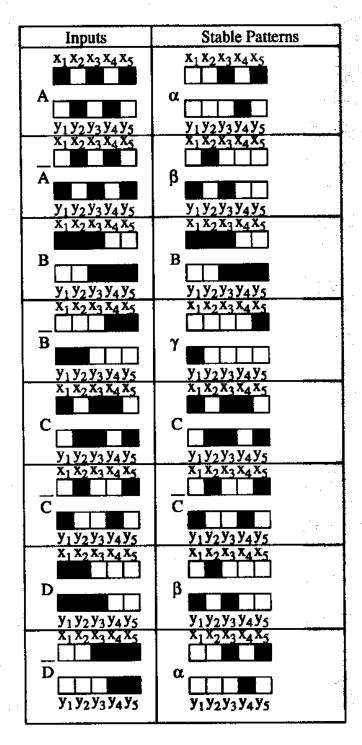

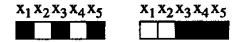

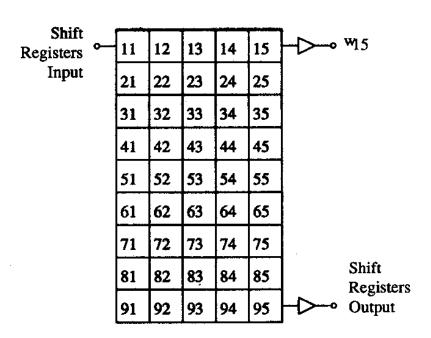

| 149    | Two Pair of Patterns to Be Stored into a $5 \times 5$ BAM                                                                                                 | 169   |

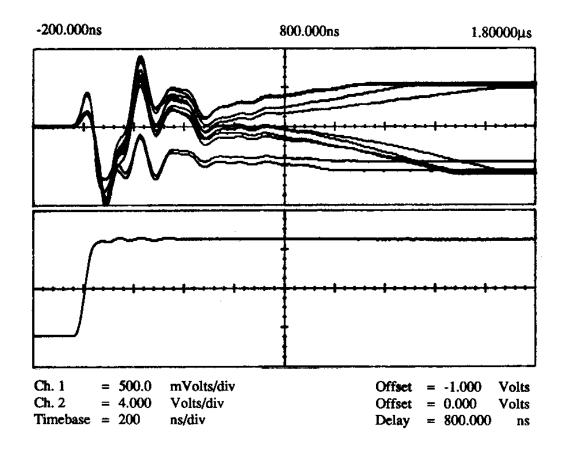

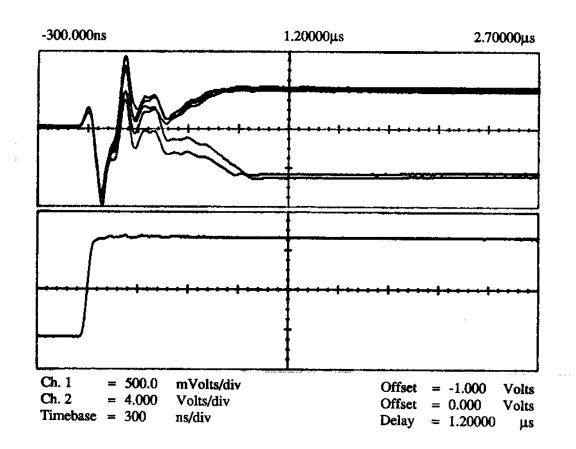

| 150    | Convergence to Pattern A When the Input Is Pattern A in BAM with Positive/Negative OTA Synaptic Matrix                                                    | . 170 |

| 151    | Complementary Patterns Also Stored in the $5 \times 5$ BAM                                                                                                | . 170 |

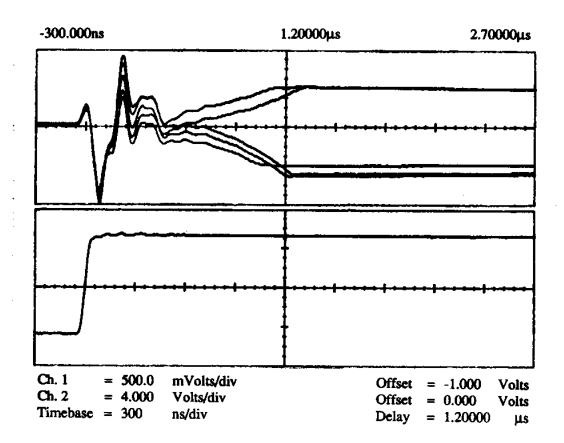

| 152    | Convergence to Pattern $\bar{A}$ When the Input Is Pattern $\bar{A}$ in BAM with Positive/Negative OTA Synaptic Matrix                                    | . 171 |

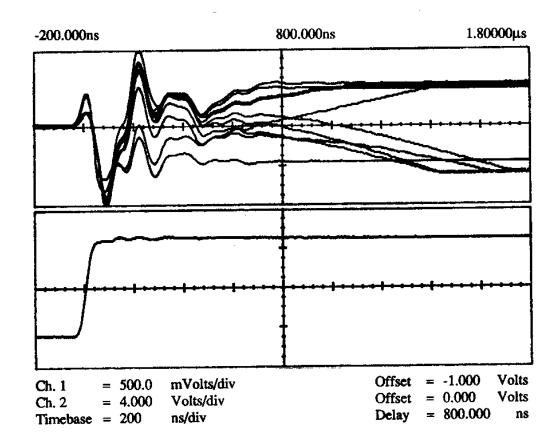

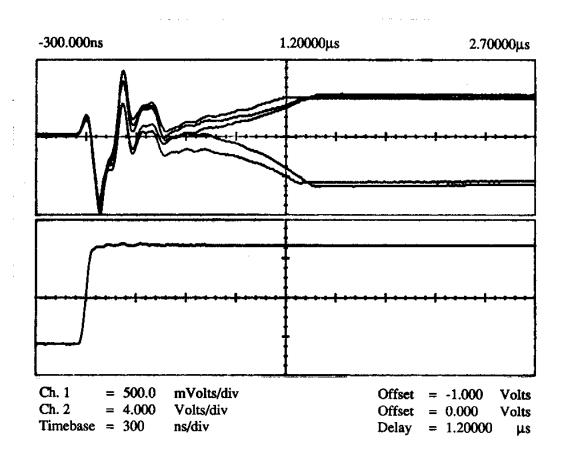

| 153    | Convergence to Pattern B When the Input Is Pattern B in BAM with Positive/Negative OTA Synaptic Matrix                                                    | . 172 |

| 154    | Convergence to Pattern $\bar{B}$ When the Input Is Pattern $\bar{B}$ in BAM with Positive/Negative OTA Synaptic Matrix                                    | . 173 |

| 155    | Convergence to Pattern B When the Inputs Are Zero in BAM with Positive/Negative OTA Synaptic Matrix                                                       | . 174 |

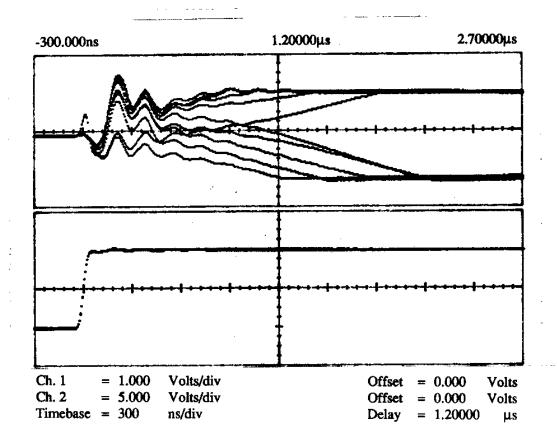

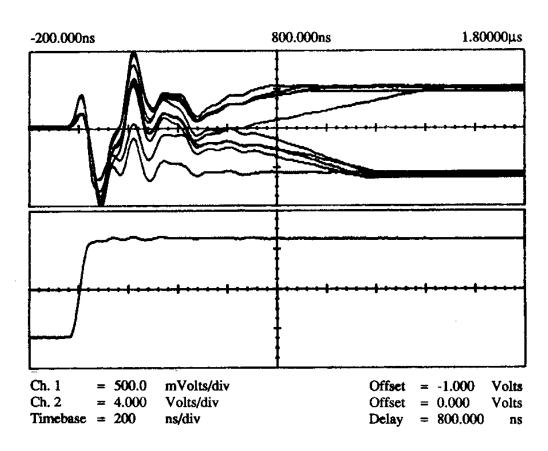

| 156    | Convergence to Pattern A When the Input Is Pattern A in BAM with Multiplier Synaptic Matrix and $V_{bias} = -4.00V$ for 2 Stored                          | . 176 |

| 157    | Patterns                                                                                                                                                  | . 170 |

| 158    | Convergence to Pattern $B$ When the Input Is Pattern $B$ in BAM with Multiplier Synaptic Matrix and $V_{bias} = -4.00V$ for 2 Stored Patterns             | . 178 |

| 159    | Convergence to Pattern $\bar{B}$ When the Input Is Pattern $\bar{B}$ in BAM with Multiplier Synaptic Matrix and $V_{bias} = -4.00V$ for 2 Stored Patterns | . 179 |

| FIGURE |                                                                                                                                                               | F    | age           |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|

| 160    | Convergence to Pattern $\bar{B}$ without Any Inputs in BAM with Multiplier Synaptic Matrix and $V_{bias}=-4.00V$ for 2 Stored Patterns                        | • •. | 180           |

| 161    | Convergence to Pattern A When the Input Is Pattern A in BAM with Multiplier Synaptic Matrix and $V_{bias} = -3.77V$ for 2 Stored Patterns                     |      | 181           |

| 162    | Convergence to Pattern $\bar{A}$ When the Input Is Pattern $\bar{A}$ in BAM with Multiplier Synaptic Matrix and $V_{bias} = -3.77V$ for 2 Stored Patterns     |      | 1 <b>8</b> 2  |

| 163    | Convergence to Pattern $B$ When the Input Is Pattern $B$ in BAM with Multiplier Synaptic Matrix and $V_{bias} = -3.77V$ for 2 Stored Patterns                 |      | 183           |

| 164    | Convergence to Pattern $\tilde{B}$ When the Input Is Pattern $\tilde{B}$ in BAM with Multiplier Synaptic Matrix and $V_{bias} = -3.77V$ for 2 Stored Patterns |      | 184           |

| 165    | Convergence to Pattern $\bar{B}$ without Any Inputs in BAM with Multiplier Synaptic Matrix and $V_{bias} = -3.77V$ for 2 Stored Patterns                      |      | 185           |

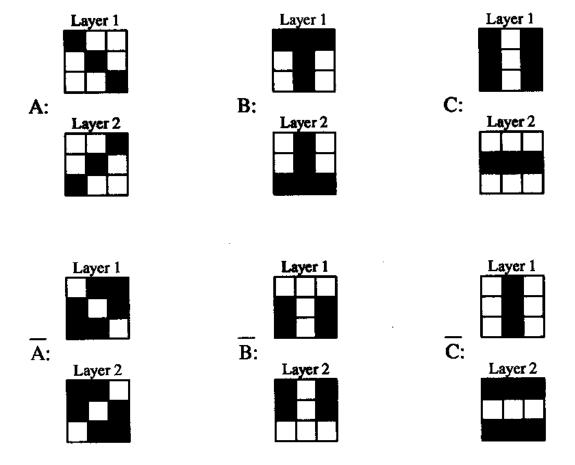

| 166    | Three Pair of Patterns (and Their Complementaries) to Be Stored in the $5 \times 5$ BAM                                                                       |      | 186           |

| 167    | Convergence to Pattern A When the Input Is Pattern A in BAM with Multiplier Synaptic Matrix and $V_{bias} = -3.77V$ for 3 Stored Patterns                     |      | 187           |

| 168    | Convergence to Pattern $\bar{A}$ When the Input Is Pattern $\bar{A}$ in BAM with Multiplier Synaptic Matrix and $V_{bias} = -3.77V$ for 3 Stored Patterns     |      | 188           |

| 169    | Convergence to Pattern $B$ When the Input Is Pattern $B$ in BAM with Multiplier Synaptic Matrix and $V_{bias} = -3.77V$ for 3 Stored Patterns                 |      | 189           |

| 170    | Convergence to Pattern $\bar{B}$ When the Input Is Pattern $\bar{B}$ in BAM with Multiplier Synaptic Matrix and $V_{bias} = -3.77V$ for 3 Stored Patterns     |      | 190           |

| 171    | Convergence to Pattern $C$ When the Input Is Pattern $C$ in BAM with Multiplier Synaptic Matrix and $V_{bias} = -3.77V$ for 3 Stored Patterns                 | • •  | . <b>19</b> 1 |

| FIGUR      | €<br>·                                                                                                                                                    | Page |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <b>172</b> | Convergence to Pattern $\bar{C}$ When the Input Is Pattern $\bar{C}$ in BAM with Multiplier Synaptic Matrix and $V_{bias} = -3.77V$ for 3 Stored Patterns | 192  |

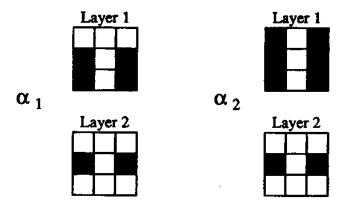

| 173        | Four Pair of Patterns (and Their Complementary) to Be Programmed into the 5 × 5 BAM                                                                       | 193  |

| 174        | Stable Output Patterns Induced by the Four Programmed Patterns and Their Complementaries                                                                  | 195  |

| 175        | Stable States Generated by the Complementary Patterns of the New Ones $\alpha$ , $\beta$ and $\gamma$ of Fig. 174                                         | 196  |

| 176        | Stable Pattern $\alpha$ Obtained When the Input A Is Disconnected                                                                                         | 197  |

| 177        | Stable Pattern $\beta$ Obtained When the Input $\bar{A}$ Is Disconnected                                                                                  | 198  |

| 178        | Stable Pattern $\gamma$ Obtained When the Input $\bar{B}$ Is Disconnected                                                                                 | 199  |

| 179        | Stable Pattern $\beta$ Obtained When the Input $D$ Is Disconnected                                                                                        | 200  |

| 180        | Stable Pattern $\alpha$ Obtained When the Input $ar{D}$ Is Disconnected                                                                                   | 201  |

| 181        | Patterns to Be Stored in the 9 × 9 BAM                                                                                                                    | 202  |

| 182        | Stable States Found in the 9 × 9 BAM When Programmed with the Patterns of Fig. 181                                                                        | 204  |

| 183        | Convergence to Pattern A with Input A in $9 \times 9$ BAM                                                                                                 | 205  |

| 184        | Convergence to Pattern $\bar{A}$ with Input $\bar{A}$ in $9 \times 9$ BAM                                                                                 | 206  |

| 185        | Convergence to Pattern $B$ with Input $B$ in $9 \times 9$ BAM                                                                                             | 207  |

| 186        | Convergence to Pattern $\alpha_1$ with Input $\bar{B}$ in $9 \times 9$ BAM                                                                                | 208  |

| 187        | Convergence to Pattern $\alpha_2$ with Input $C$ in $9 \times 9$ BAM                                                                                      | 209  |

| 188        | Convergence to Pattern $\bar{C}$ with Input $\bar{C}$ in $9 \times 9$ BAM                                                                                 | 210  |

| 189        | Stable States of $9 \times 9$ BAM When Compensated for Offset Currents                                                                                    | 212  |

| 190        | Convergence to Pattern A with Input A in Offset Compensated $9 \times 9$ BAM (Only Layer 1 Is Shown)                                                      | 213  |

| 191        | Convergence to Pattern A with Input A in Offset Compensated $9 \times 9$ BAM (Only Layer 2 Is Shown)                                                      | 214  |

| 192        | Convergence to Pattern $\bar{A}$ with Input $\bar{A}$ in Offset Compensated $9 \times 9$ BAM (Only Layer 1 Is Shown)                                      | 215  |

| FIGURI | 3                                                                                                                         | Page          |

|--------|---------------------------------------------------------------------------------------------------------------------------|---------------|

| 193    | Convergence to Pattern $\bar{A}$ with Input $\bar{A}$ in Offset Compensated $9 \times 9$ BAM (Only Layer 2 Is Shown)      | . 216         |

| 194    | Convergence to Pattern $B$ with Input $B$ in Offset Compensated $9 \times 9$ BAM (Only Layer 1 Is Shown)                  | . 217         |

| 195    | Convergence to Pattern $B$ with Input $B$ in Offset Compensated $9 \times 9$ BAM (Only Layer 2 Is Shown)                  | . <b>21</b> 8 |

| 196    | Convergence to Pattern $\bar{B}$ with Input $\bar{B}$ in Offset Compensated $9 \times 9$ BAM (Only Layer 1 Is Shown)      | . 219         |

| 197    | Convergence to Pattern $\bar{B}$ with Input $\bar{B}$ in Offset Compensated $9 \times 9$ BAM (Only Layer 2 Is Shown)      |               |

| 198    | Convergence to Pattern $C$ with Input $C$ in Offset Compensated $9 \times 9$ BAM (Only Layer 1 Is Shown)                  |               |

| 199    | Convergence to Pattern $C$ with Input $C$ in Offset Compensated $9 \times 9$ BAM (Only Layer 2 Is Shown)                  |               |

| 200    | Convergence to Pattern $\bar{C}$ with Input $\bar{C}$ in Offset Compensated $9 \times 9$ BAM (Only Layer 1 Is Shown)      |               |

| 201    | Convergence to Pattern $\bar{C}$ with Input $\bar{C}$ in Offset Compensated $9 \times 9$ BAM (Only Layer 2 Is Shown)      |               |

| 202    | Hopfield Network Built with T-Mode BAM's Modular Chip Components; (a) Interconnection Strategy, (b) Resulting Hopfield T- |               |

|        | Mode Circuit                                                                                                              |               |

| 203    | Pattern to Be Stored in the 5-Neuron Hopfield Circuit                                                                     | . 226         |

| 204    | Convergence to Pattern 10101 (21) with Input 10101 (21) in the T-Mode Hopfield Network                                    | . 227         |

| 205    | Convergence to Pattern 01010 (10) with Input 01010 (10) in the T-Mode Hopfield Network                                    | . 228         |

| 206    | Convergence to Pattern 10101 (21) without Any Input in the T-Mode Hopfield Network                                        | . 229         |

| 207    | Measured Stable States for Hopfield Circuit Loaded with the Pattern of Fig. 203                                           | . 230         |

| 208    | Two Patterns to Be Stored in the 5-Neuron Hopfield Circuit                                                                |               |

| FIGURE |                                                                                                                                                                                                                                                            | Page  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 209    | Measured Stable States for Hopfield Circuit Loaded with Patterns of Fig. 208                                                                                                                                                                               | . 232 |

| 210    | Convergence to Pattern (16) with Input (27) for Hopfield T-Mode<br>Circuit with 2 Stored Patterns                                                                                                                                                          | . 233 |

| 211    | Winner-Take-All Interconnection Topology                                                                                                                                                                                                                   | . 234 |

| 212    | Two-Quadrant Synaptic Multipliers Needed for the Winner-Take-All T-Mode Implementation                                                                                                                                                                     | . 235 |

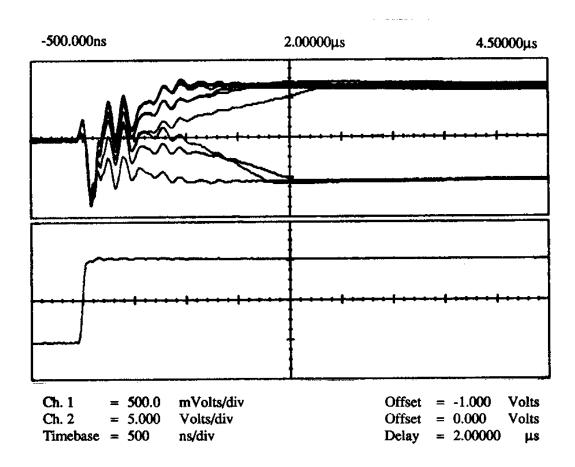

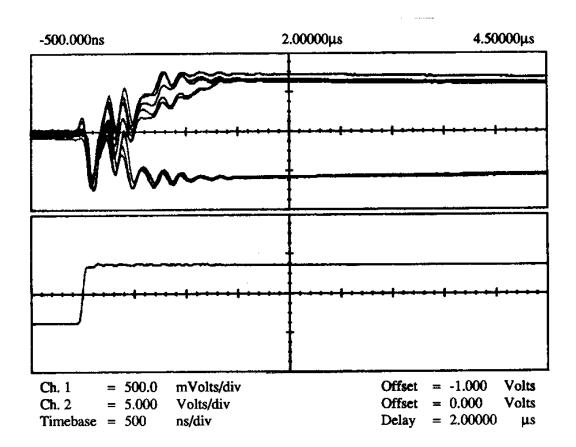

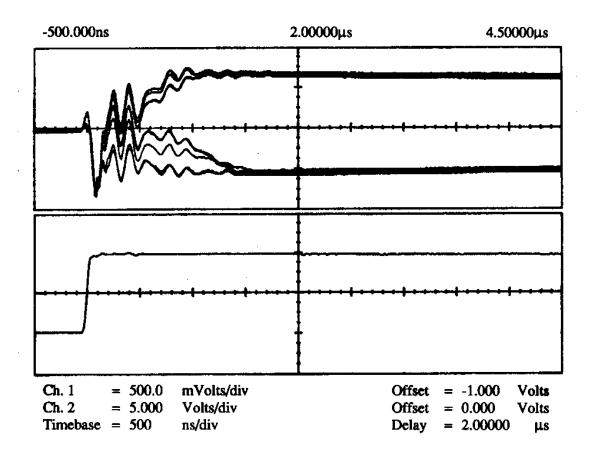

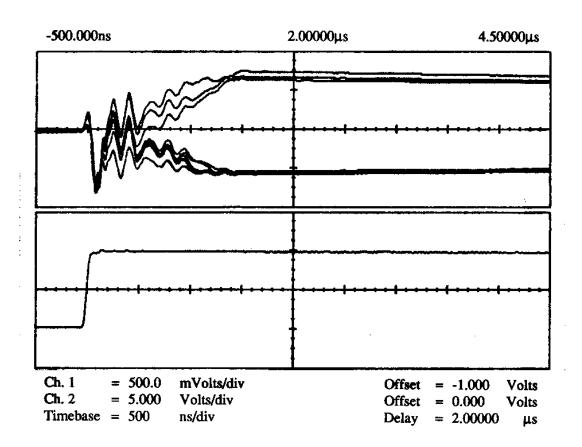

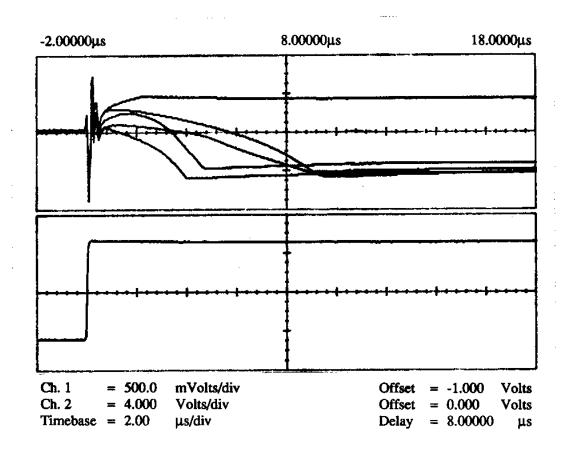

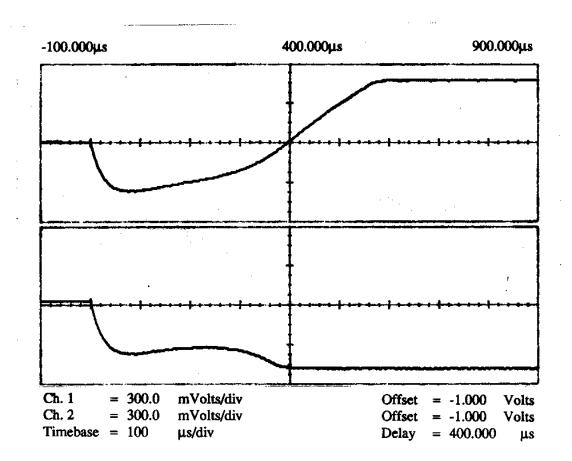

| 213    | Winner-Take-All T-Mode Circuit with Input (10010); The Two Traces Correspond to Neurons $x_1$ and $x_4$ , The Integrating Capacitance of Each Neuron Is $10nF$ , $V_{bias} = -3.77V$ , $GND_{bottom} = -2.00V$ , $GND_{top} = E^- = -1.5V$ , $E^+ = -0.5V$ | . 237 |

| 214    | Interconnection Topology for Simplified Grossberg Network Using the BAM Modular Chips                                                                                                                                                                      | . 238 |

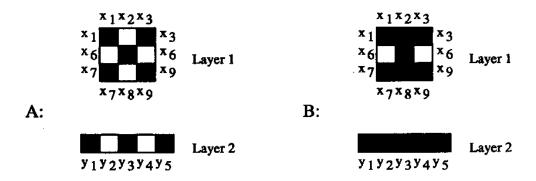

| 215    | Five Patterns to Be Stored in the Simplified Grossberg Network                                                                                                                                                                                             | . 239 |

| 216    | Stable Patterns Obtained for the Simplified Grossberg Network                                                                                                                                                                                              | . 241 |

| 217    | Convergence to Pattern A in Layer 1 with Input A for Simplified Grossberg Network                                                                                                                                                                          | . 242 |

| 218    | Convergence to Pattern A in Layer 2 with Input A for Simplified Grossberg Network                                                                                                                                                                          | . 243 |

| 219    | Convergence to Pattern B in Layer 1 with Input B for Simplified Grossberg Network                                                                                                                                                                          | . 244 |

| 220    | Convergence to Pattern B in Layer 2 with Input B for Simplified Grossberg Network                                                                                                                                                                          | . 245 |

| 221    | Convergence to Pattern $C$ in Layer 1 with Input $C$ for Simplified Grossberg Network                                                                                                                                                                      | . 246 |

| 222    | Convergence to Pattern $C$ in Layer 2 with Input $C$ for Simplified Grossberg Network                                                                                                                                                                      | . 247 |

| 223    | Convergence to Pattern $D$ in Layer 1 with Input $D$ for Simplified Grossberg Network                                                                                                                                                                      | . 248 |

| 224    | Convergence to Pattern D in Layer 2 with Input D for Simplified Grossberg Network                                                                                                                                                                          | . 249 |

| FIGURI | E 1                                                                                                                               | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------|------|

| 225    | Convergence to Pattern E in Layer 1 with Input E for Simplified  Grossberg Network                                                | 250  |

| 226    | Convergence to Pattern E in Layer 2 with Input E for Simplified Grossberg Network                                                 | 251  |

| 227    | Normalized T-Mode Optimization Circuit for Solving the Problem of Equations (5.26) and (5.27)                                     | 253  |

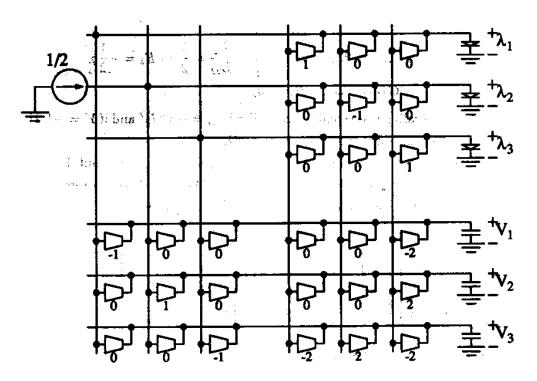

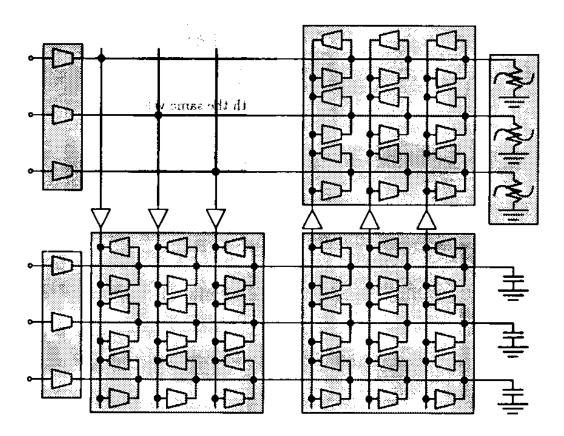

| 228    | Interconnection Topology for Optimization Circuit                                                                                 | 256  |

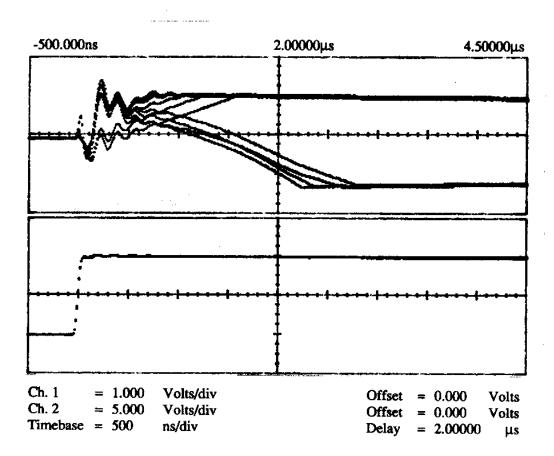

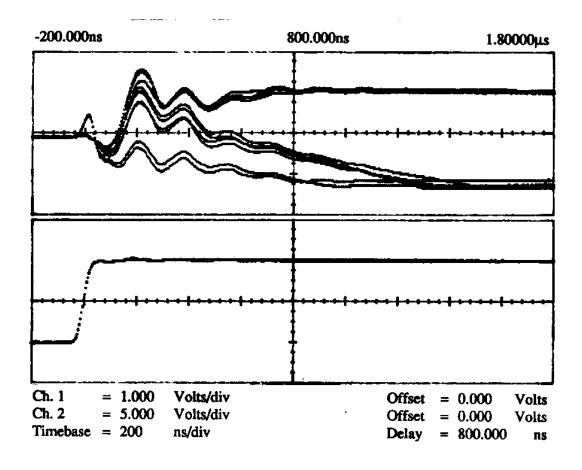

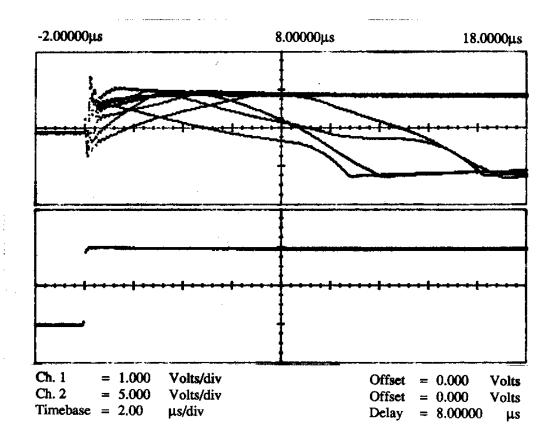

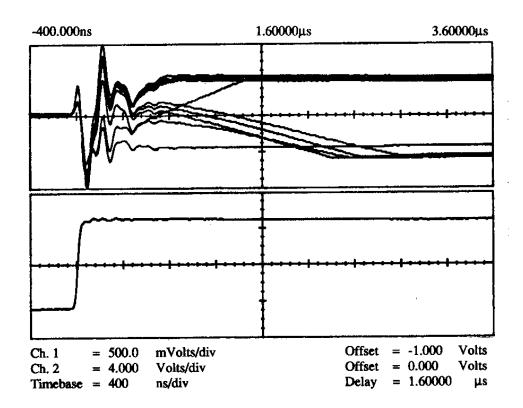

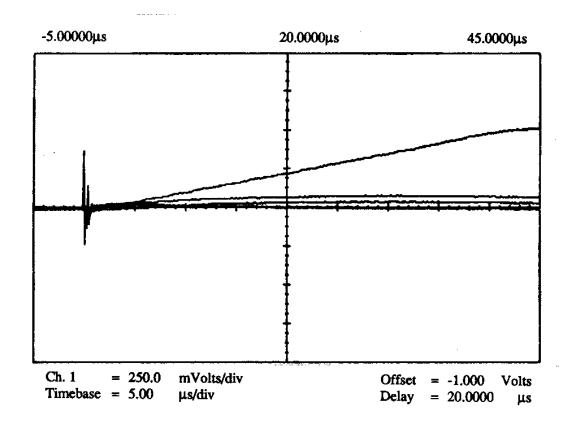

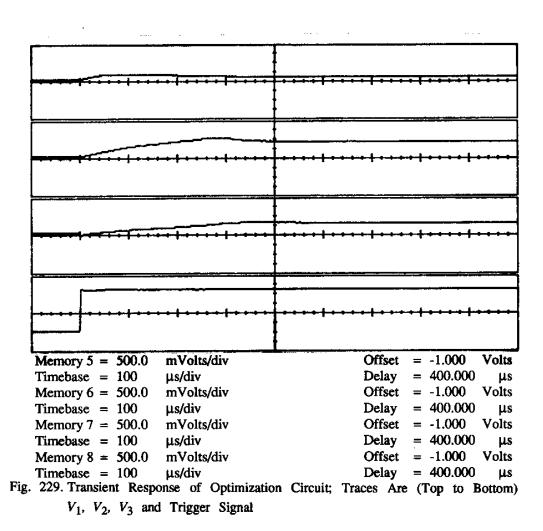

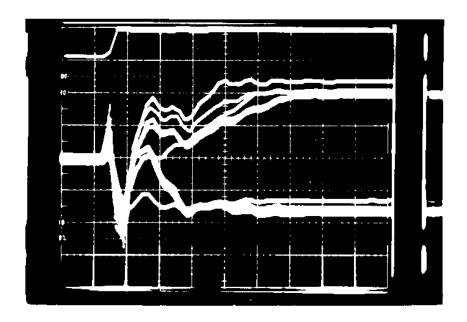

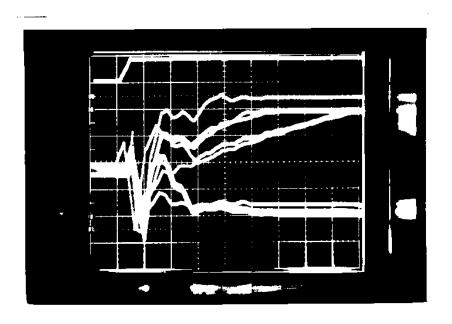

| 229    | Transient Response of Optimization Circuit; Traces Are (Top to Bottom) $V_1$ , $V_2$ , $V_3$ and Trigger Signal                   | 257  |

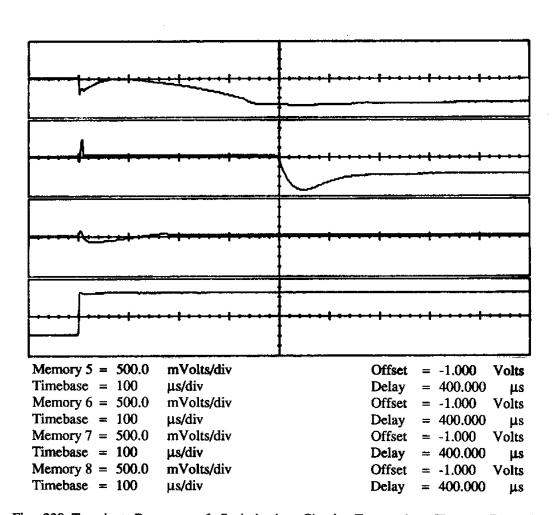

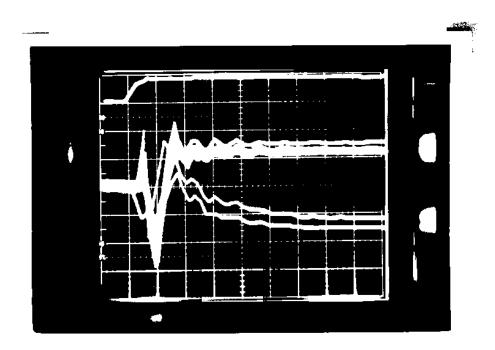

| 230    | Transient Response of Optimization Circuit; Traces Are (Top to Bottom) $\lambda_1$ , $\lambda_2$ , $\lambda_3$ and Trigger Signal | 258  |

| 231    | Input Output Behavior of Oscillatory Neuron                                                                                       | 260  |

| 232    | Interconnection Topology for Oscillatory Hopfield Network                                                                         | 261  |

| 233    | Measured Stable States for Oscillatory Hopfield Network Loaded with the Pattern 10101                                             | 262  |

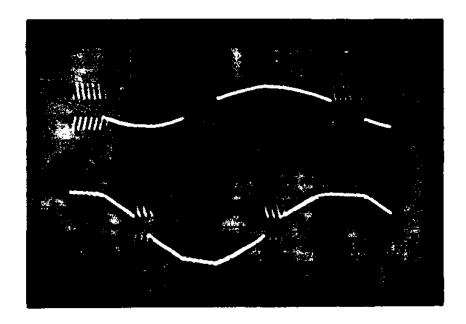

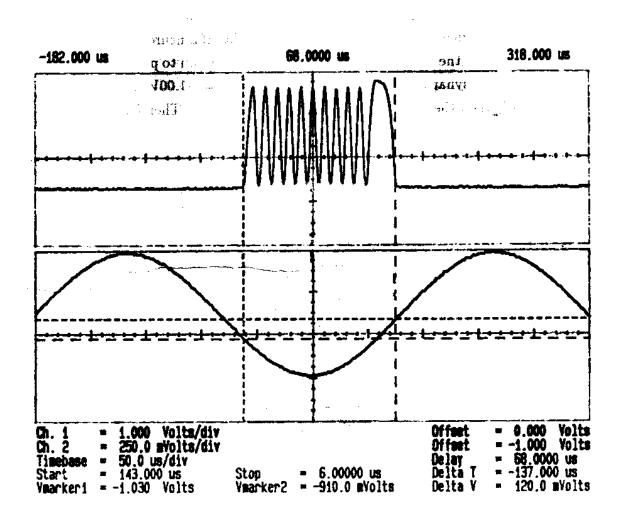

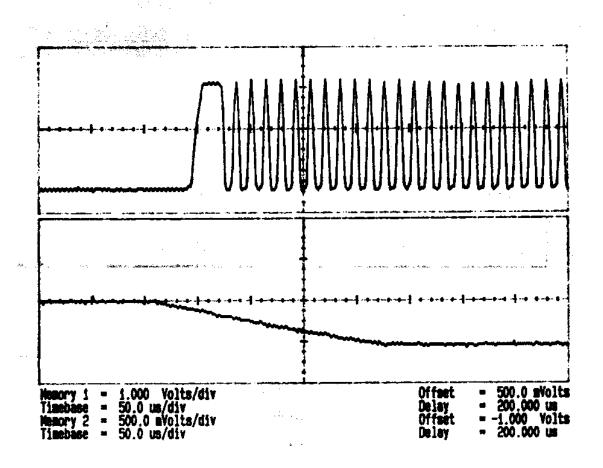

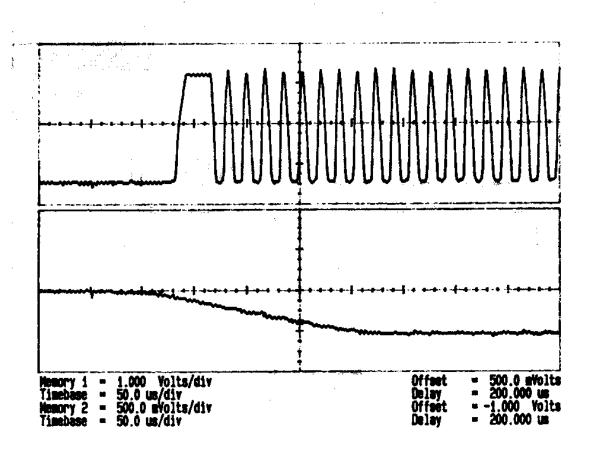

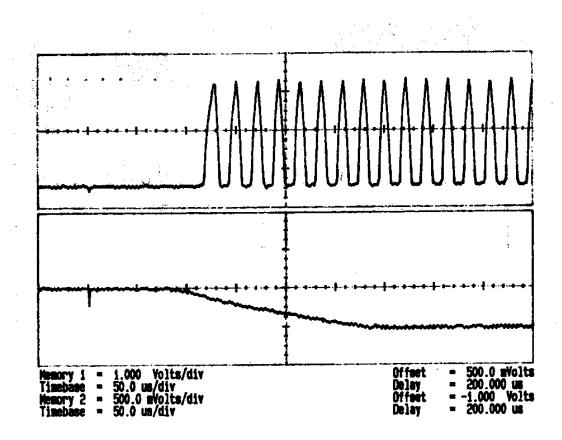

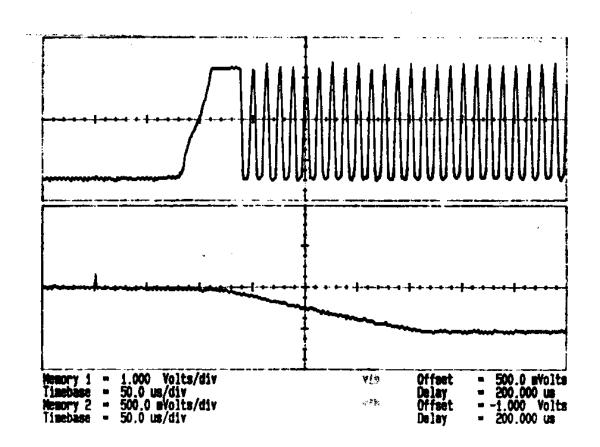

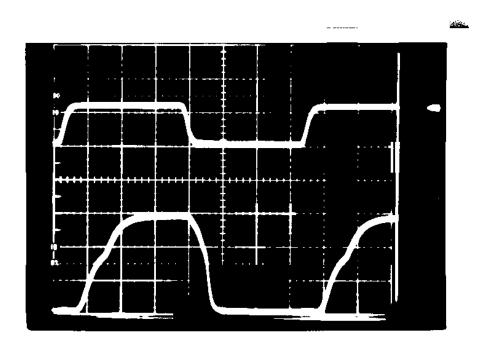

| 234    | Convergence to Pattern 10101 for Oscillatory Hopfield Network;<br>Input and Output of Neuron $x_1$ Are Shown                      | 263  |

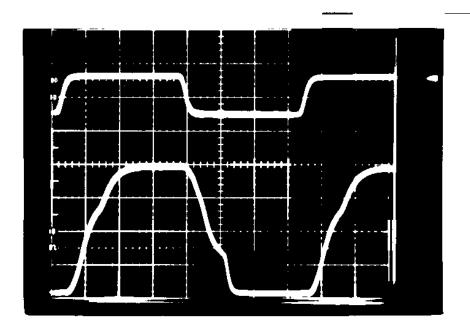

| 235    | Convergence to Pattern 10101 for Oscillatory Hopfield Network;<br>Input and Output of Neuron $x_2$ Are Shown                      | 264  |

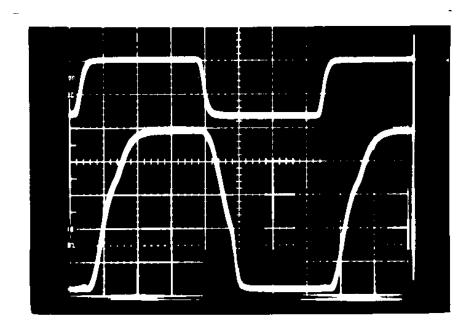

| 236    | Convergence to Pattern 10101 for Oscillatory Hopfield Network;<br>Input and Output of Neuron x <sub>3</sub> Are Shown             | 265  |

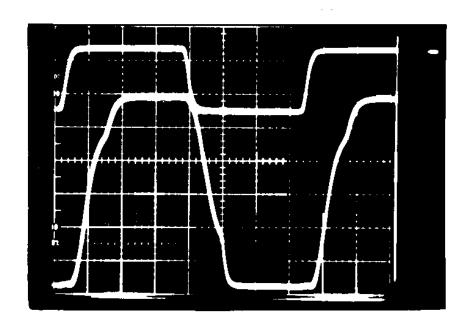

| 237    | Convergence to Pattern 10101 for Oscillatory Hopfield Network;<br>Input and Output of Neuron $x_4$ Are Shown                      | 266  |

| 238    | Convergence to Pattern 10101 for Oscillatory Hopfield Network;<br>Input and Output of Neuron $x_5$ Are Shown                      | 267  |

| 239    | Interconnection Topology for Oscillatory BAM                                                                                      | 268  |

| 240    | Pattern to Be Stored in the Oscillatory BAM                                                                                       | 268  |

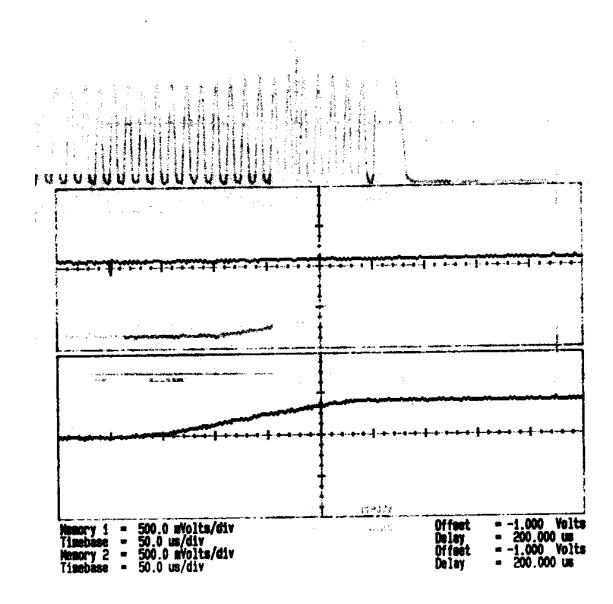

| 241    | Convergence to Pattern $A$ for Oscillatory BAM Network; Input and Output of Neuron $x_1$ Are Shown                                | 269  |

| 242    | Convergence to Pattern $A$ for Oscillatory BAM Network; Input and Output of Neuron $x_2$ Are Shown                                | 270  |

| FIGUR | E Page                                                                                                                                                                                                            |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

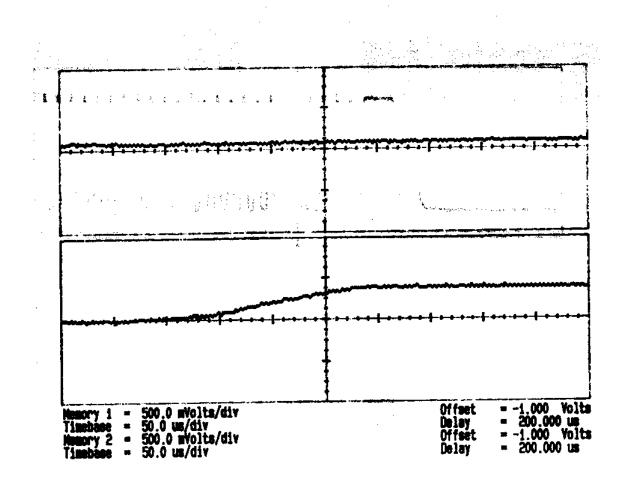

| 243   | Convergence to Pattern A for Oscillatory BAM Network; Input and Output of Neuron x <sub>3</sub> Are Shown                                                                                                         |

| 244   | Convergence to Pattern A for Oscillatory BAM Network; Input and Output of Neuron y <sub>1</sub> Are Shown                                                                                                         |

| 245   | Convergence to Pattern A for Oscillatory BAM Network; Input and Output of Neuron y <sub>2</sub> Are Shown                                                                                                         |

| 246   | Convergence to Pattern A for Oscillatory BAM Network; Input and Output of Neuron y <sub>3</sub> Are Shown                                                                                                         |

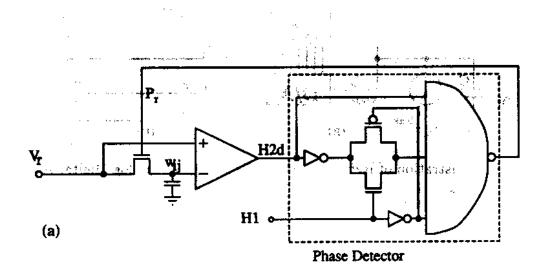

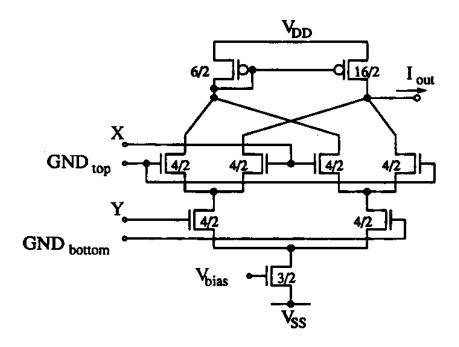

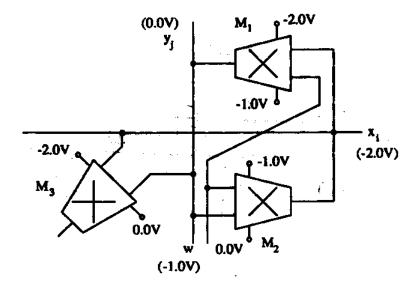

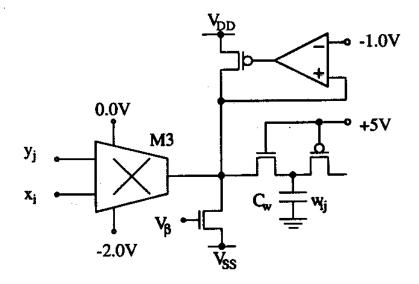

| 247   | Multiplier Circuit Used for M3                                                                                                                                                                                    |

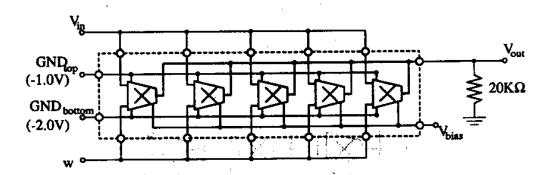

| 248   | Ground Bias Voltages for the Three Synaptic Multipliers                                                                                                                                                           |

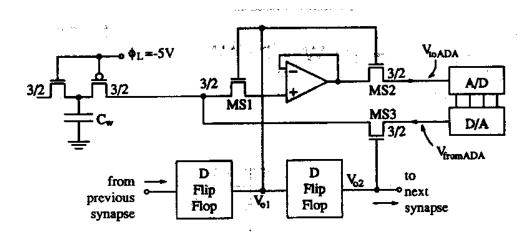

| 249   | Synaptic Weight Refreshing Circuit for Adaptive BAM 277                                                                                                                                                           |

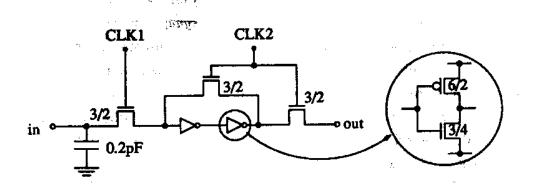

| 250   | Circuit Diagram of D-Flip-Flop                                                                                                                                                                                    |

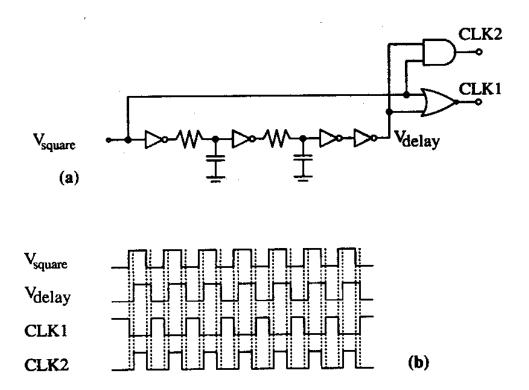

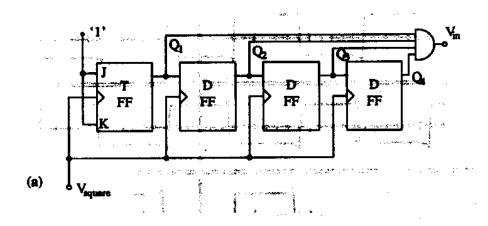

| 251   | (a) Circuit for Clock Signals Generation, (b) Waveforms                                                                                                                                                           |

| 252   | (a) Circuit for Input Signal Generation, (b) Waveforms 279                                                                                                                                                        |

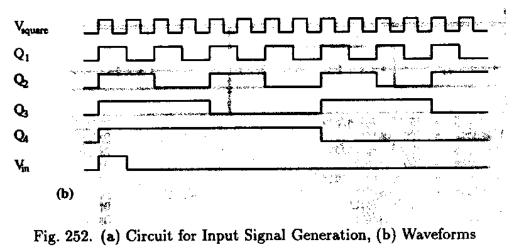

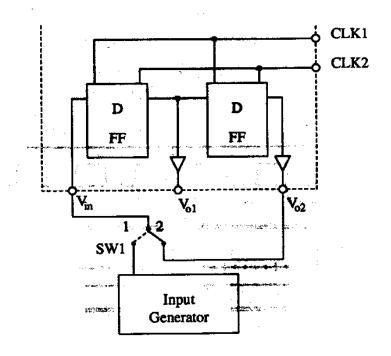

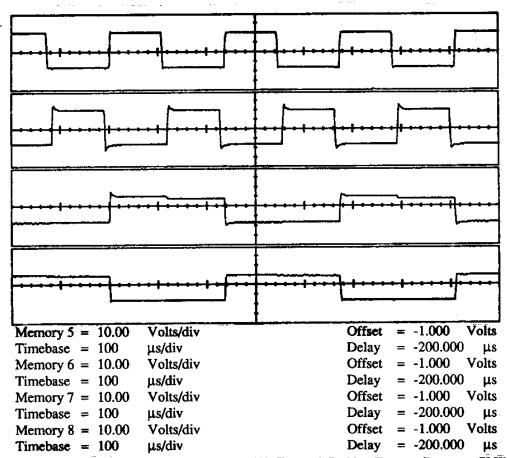

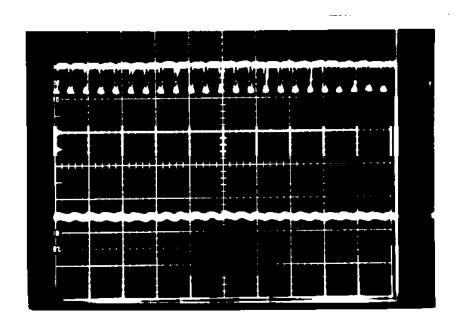

| 253   | Measured Waveforms for Shift Registers (Top to Bottom): $V_{square}$ , $CLK1, CLK2, V_{in} \ldots 280$                                                                                                            |

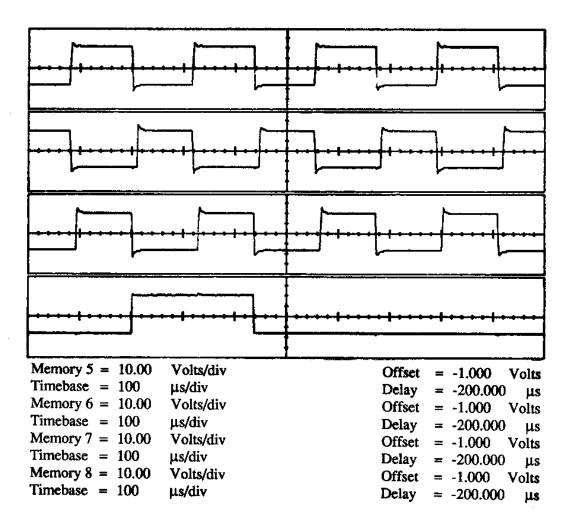

| 254   | Measured Waveforms for Shift Registers (Top to Bottom): $V_{square}$ , $V_{in}, V_{o1}, V_{o2} \dots \dots$ |

| 255   | Set Up for Shift Registers Test                                                                                                                                                                                   |

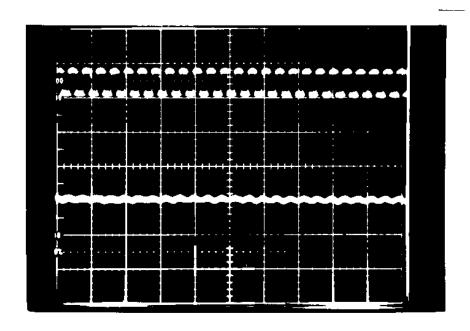

| 256   | Two D-Flip-Flops Loop with a '1' Trapped Inside; Top to Bottom:  CLK1, CLK2, Vol., Vol                                                                                                                            |

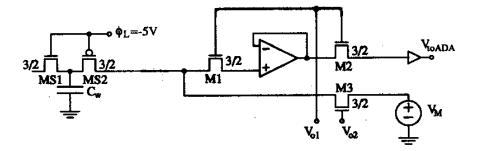

| 257   | Topology Used for Test of Refreshing Action                                                                                                                                                                       |

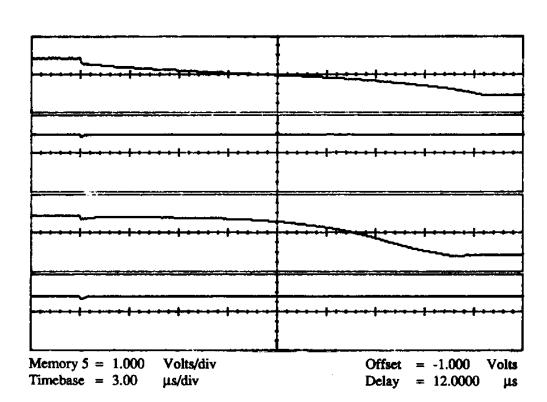

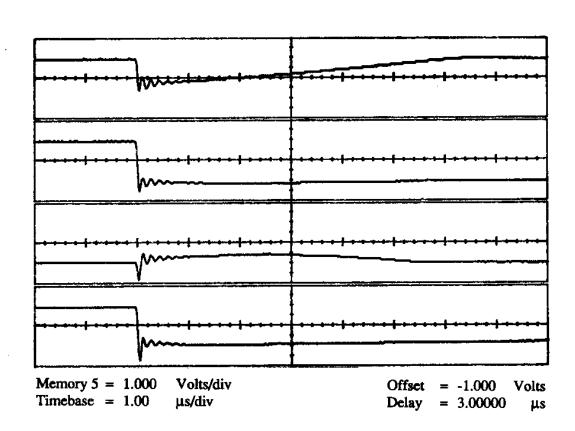

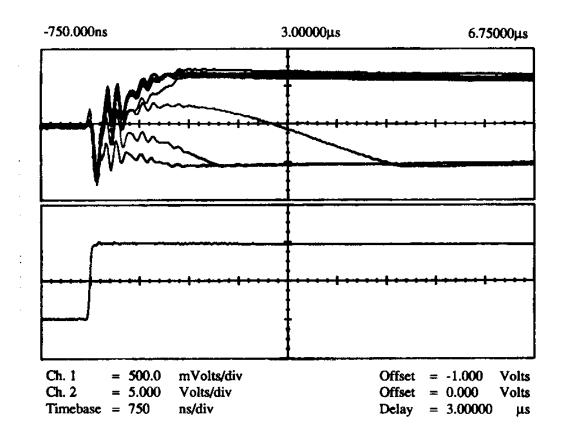

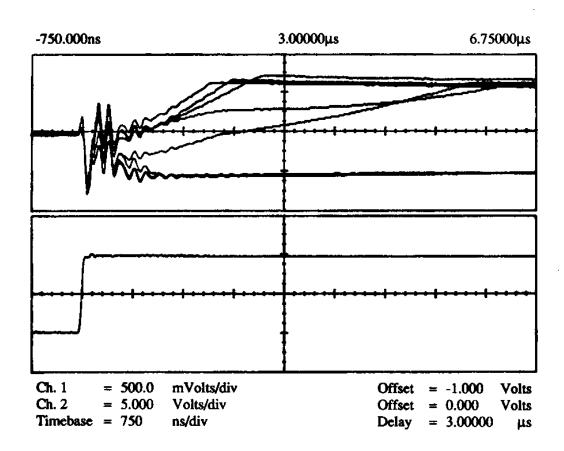

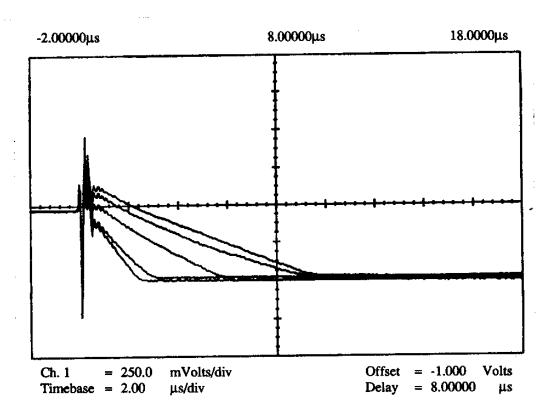

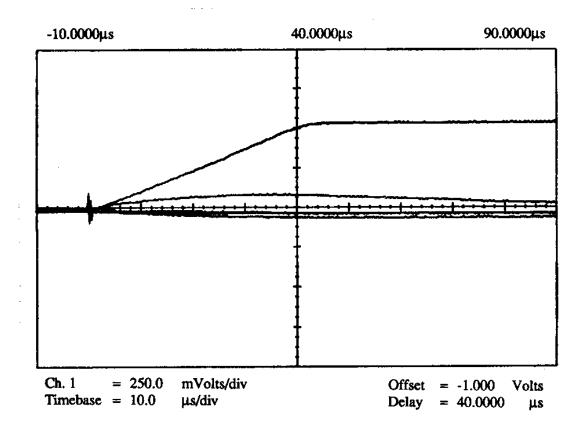

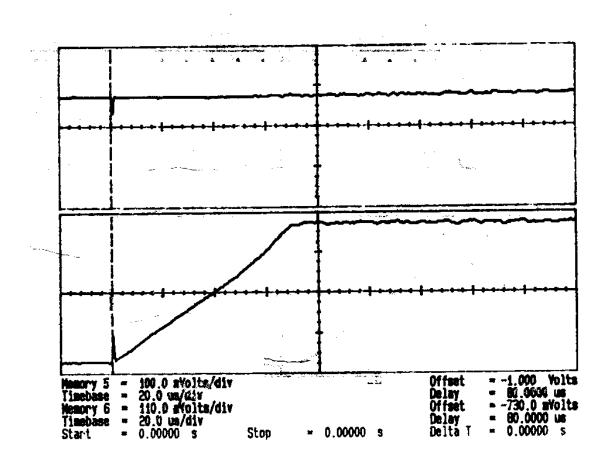

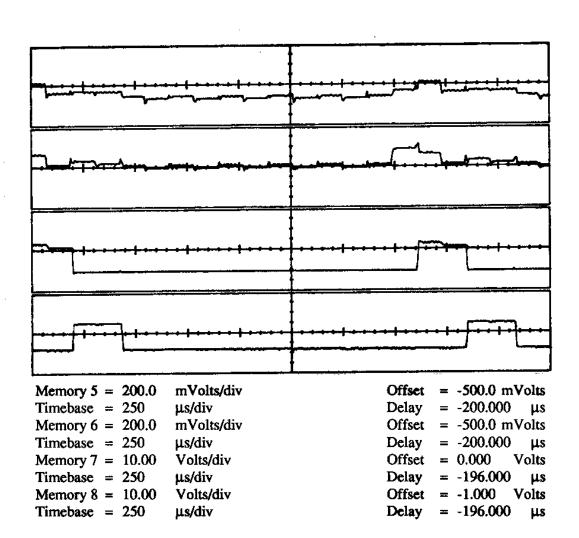

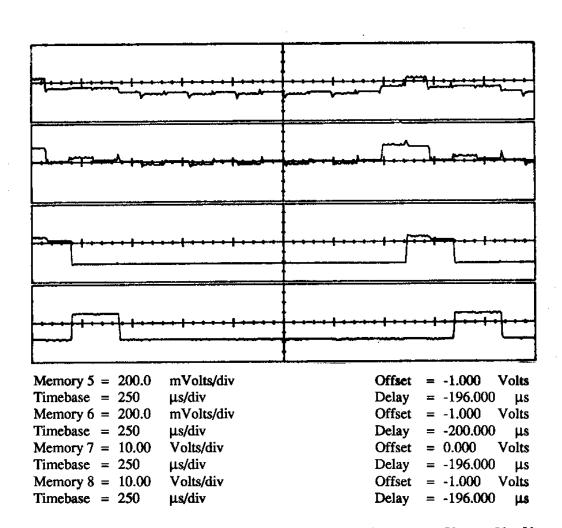

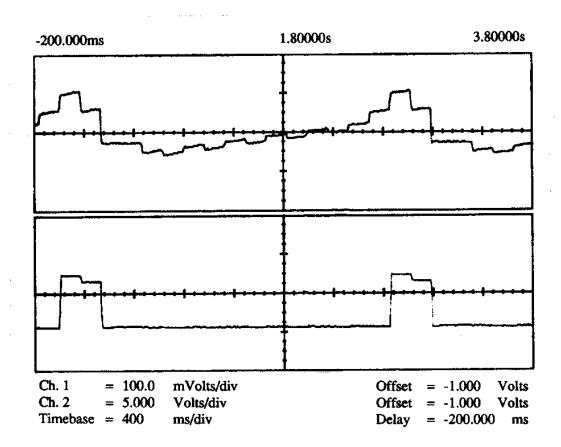

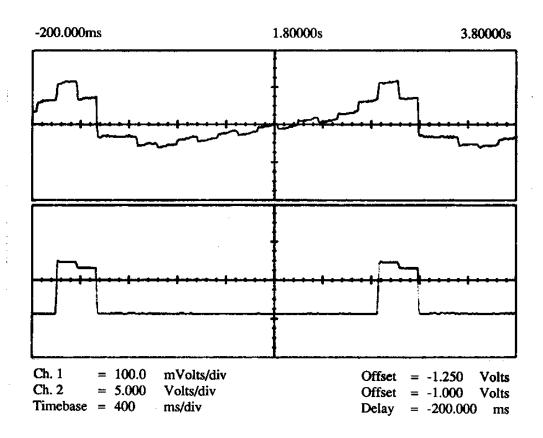

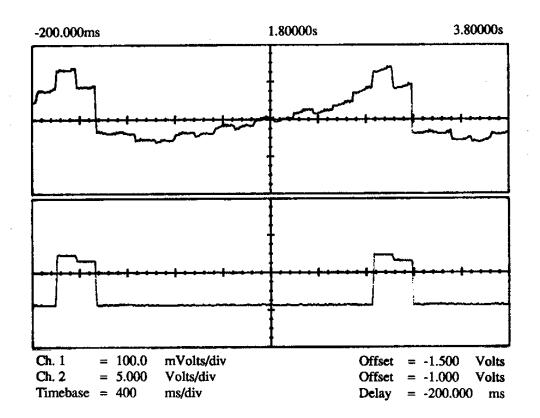

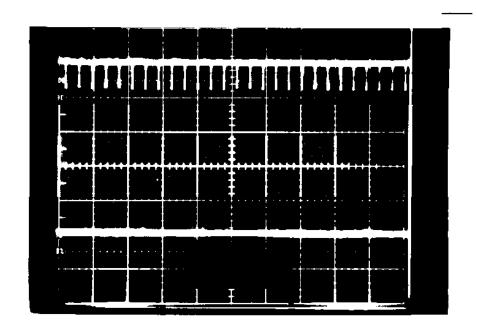

| 258   | Refreshing Action for $V_M = -0.50V$ ; Top to Bottom: $w, V_{toADA}, V_{o1}, V_{o2} \dots \dots$            |

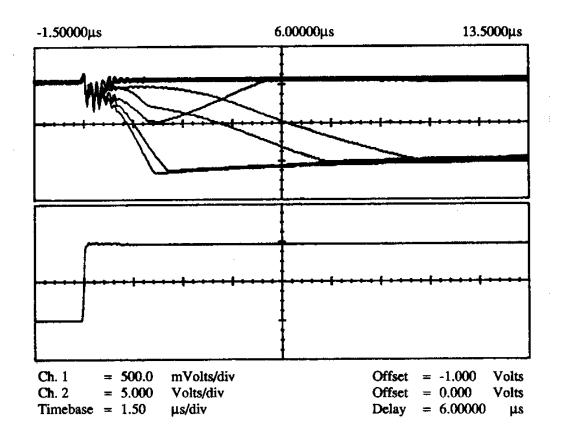

| 259   | Refreshing Action for $V_M = -1.00V$ ; Top to Bottom: $w$ , $V_{toADA}$ , $V_{o1}$ , $V_{o2}$                                                                                                                     |

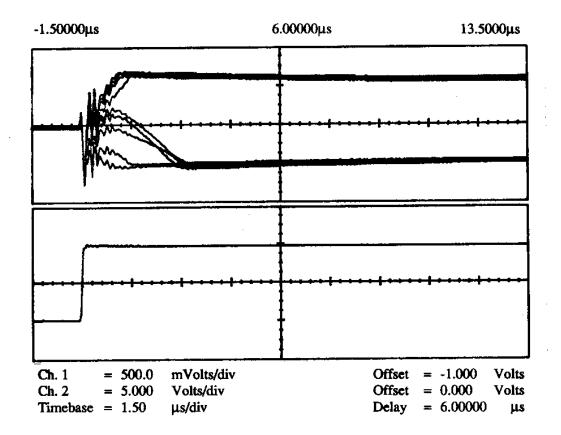

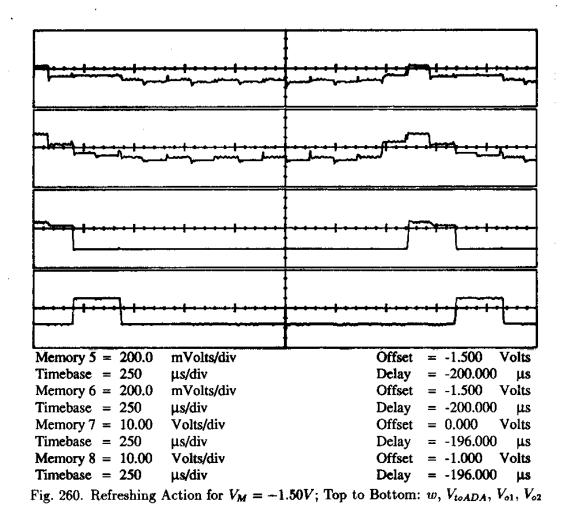

| 260   | Refreshing Action for $V_M = -1.50V$ ; Top to Bottom: $w$ , $V_{toADA}$ , $V_{o1}$ , $V_{o2}$                                                                                                                     |

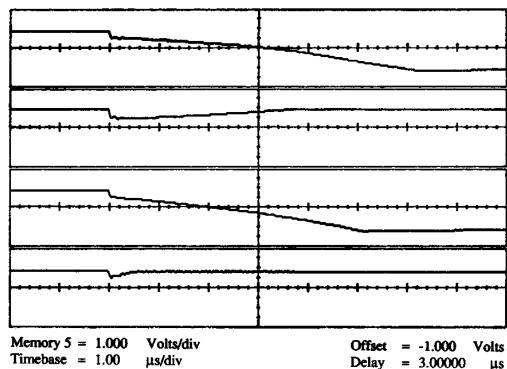

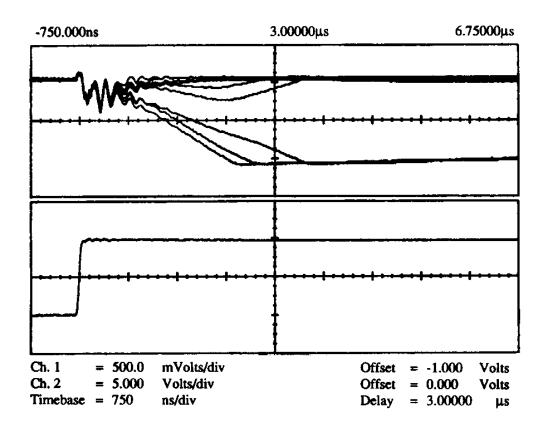

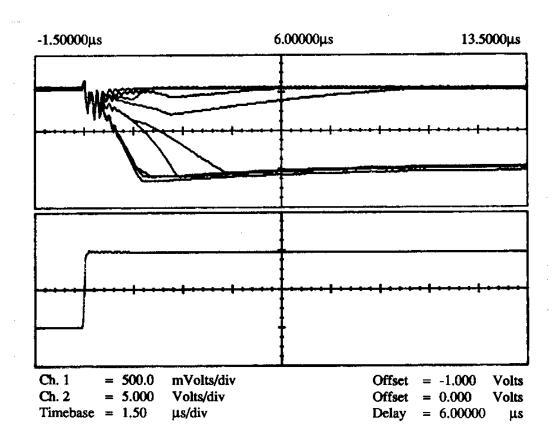

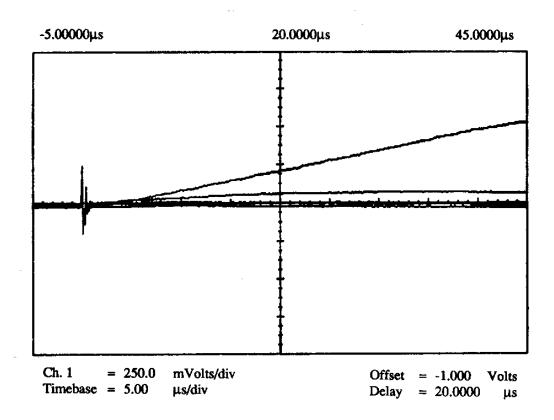

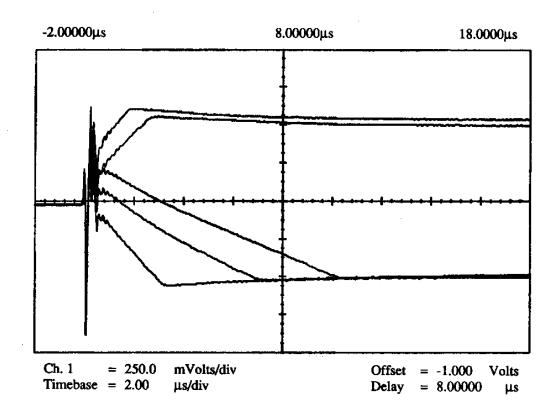

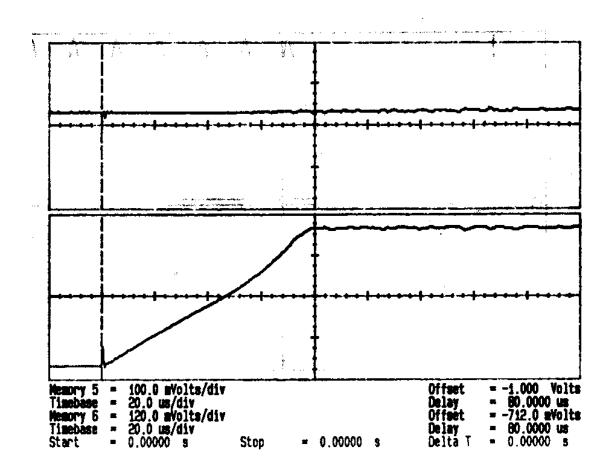

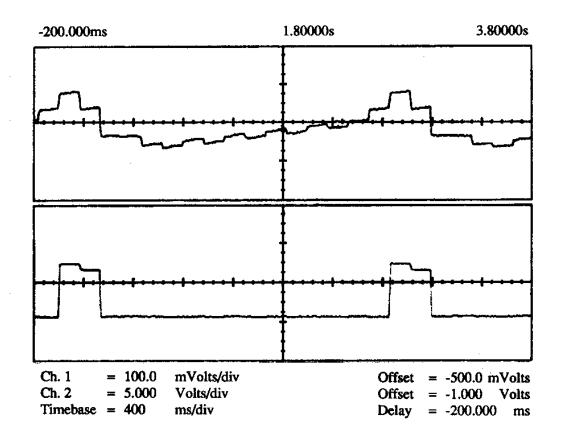

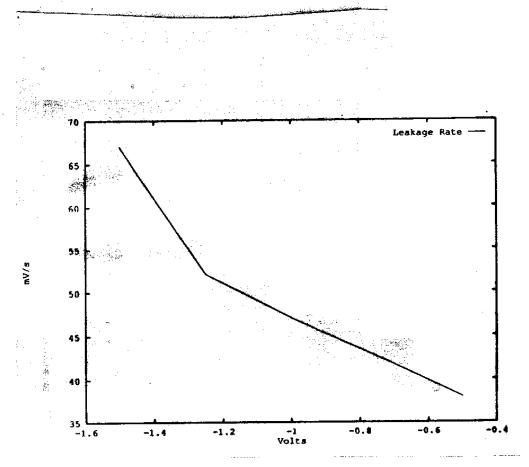

| 261   | Measurement of Leakage Rate for $V_M = -0.50V \dots 287$                                                                                                                                                          |

| 262   | Measurement of Leakage Rate for $V_M = -0.75V \dots 288$                                                                                                                                                          |

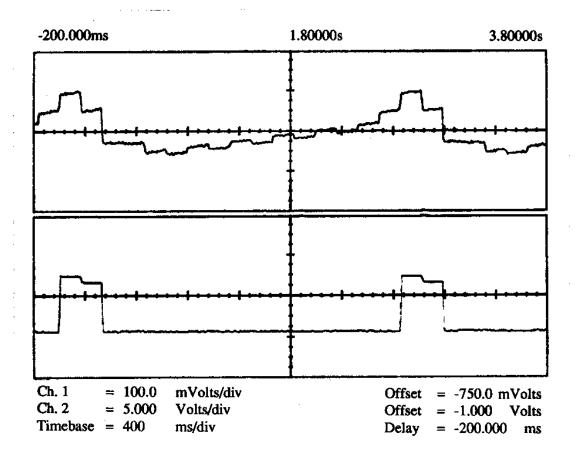

| FIGUE | RE                                                                                                                                                                                 | age |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 263   | "Measurement of Leakage Rate for $V_M = -1.00V$                                                                                                                                    | 289 |

| 264   | Measurement of Leakage Rate for $V_M = -1.25V$                                                                                                                                     | 290 |

| 265   | Measurement of Leakage Rate for $V_M = -1.50V$                                                                                                                                     | 291 |

| 266   | Plot of Leakage Rate As a Function of the Capacitor Voltage                                                                                                                        | 292 |

| 267   | Circuit Diagram of Comparator Used in ADA Converter                                                                                                                                | 292 |

| 268   | Measured DC Transfer Curve of ADA Converter; Horizontal and Vertical Scales Are $200mV/div$ , and Center Is $(-1.0V, -1.0V)$                                                       | 293 |

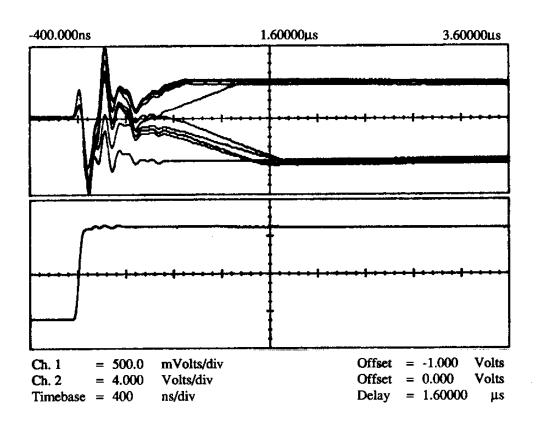

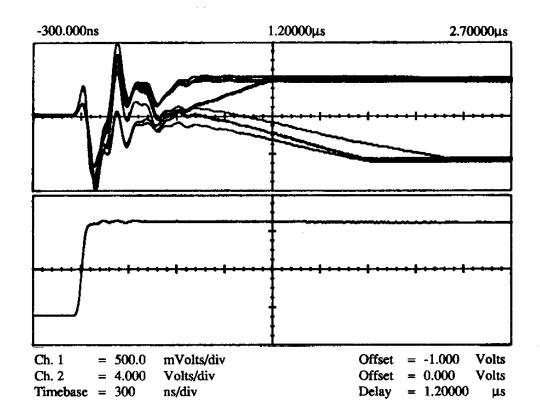

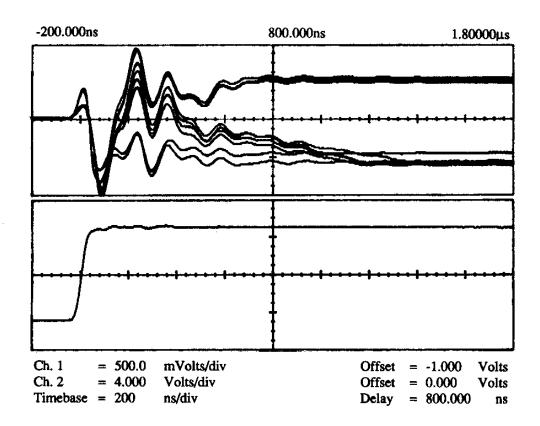

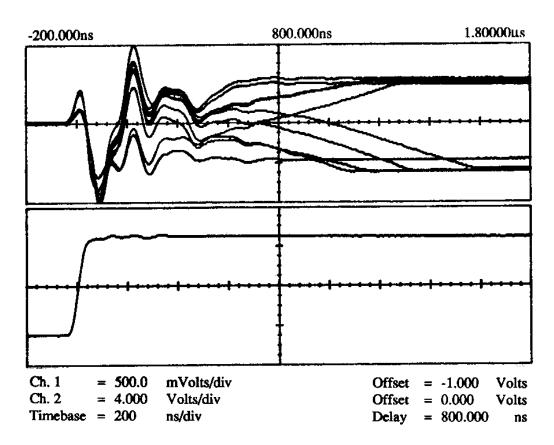

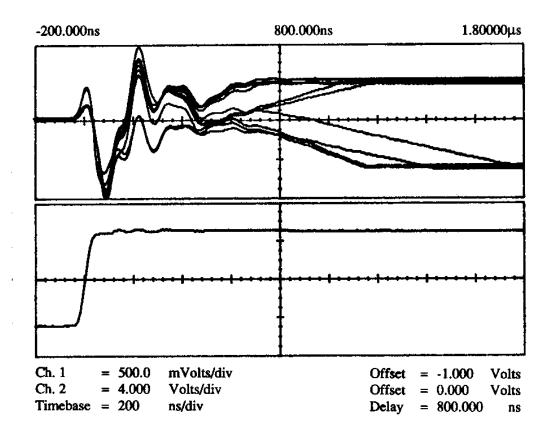

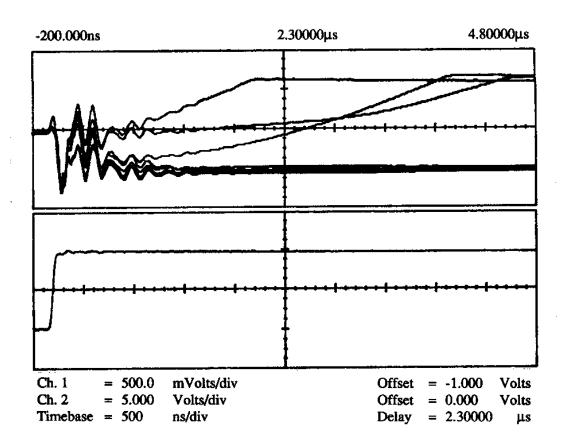

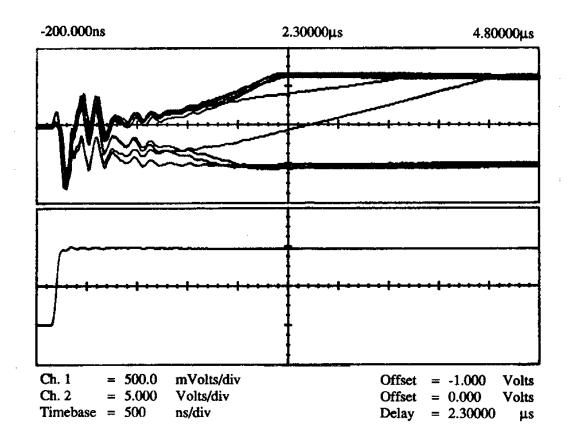

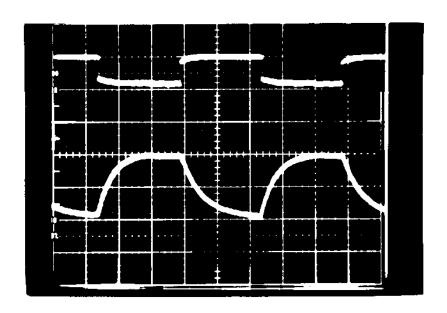

| 269   | ADA Transition from Level '0' to Level '1'; Top Trace Is Input $(500mV/div)$ , Bottom Trace Is Output $(200mV/div)$ , Offset Is $-800mV$ ; Time Scale Is $200ns/div$               | 294 |

| 270   | ADA Transition from Level '0' to Level '2'; Top Trace Is Input $(500mV/div)$ , Bottom Trace Is Output $(200mV/div)$ , Offset Is $-800mV$ ); Time Scale Is $200ms/div$              | 295 |

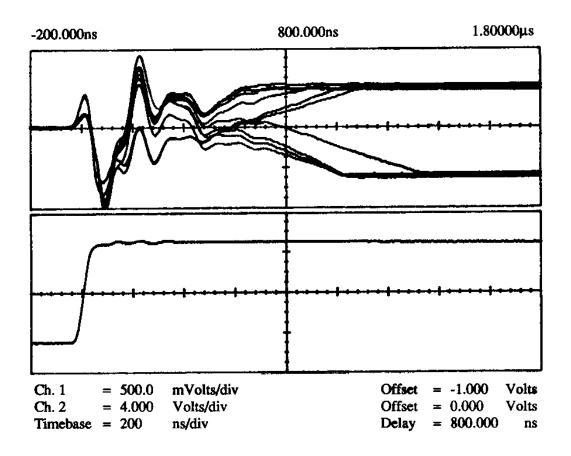

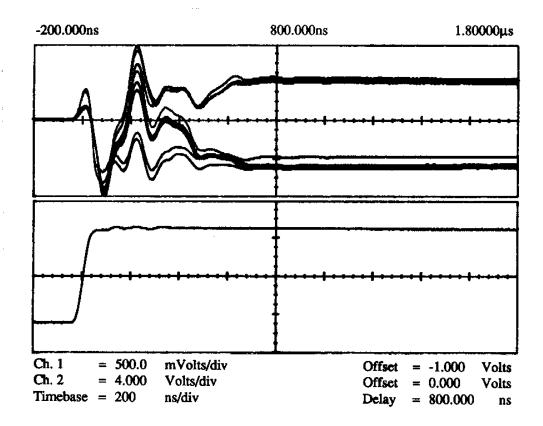

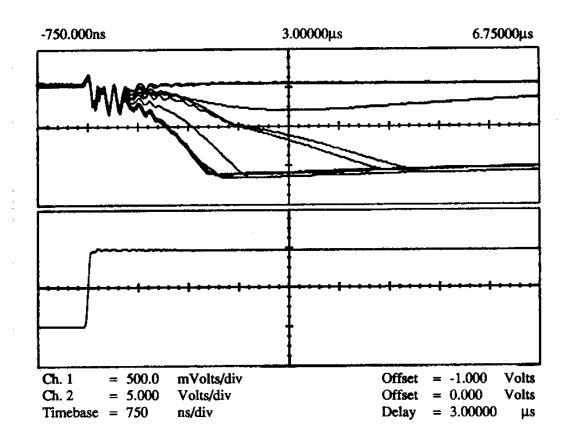

| 271   | ADA Transition from Level '0' to Level '3'; Top Trace Is Input $(500mV/div)$ , Bottom Trace Is Output $(200mV/div)$ , Offset Is $-800mV$ ); Time Scale Is $200ns/div$              | 296 |

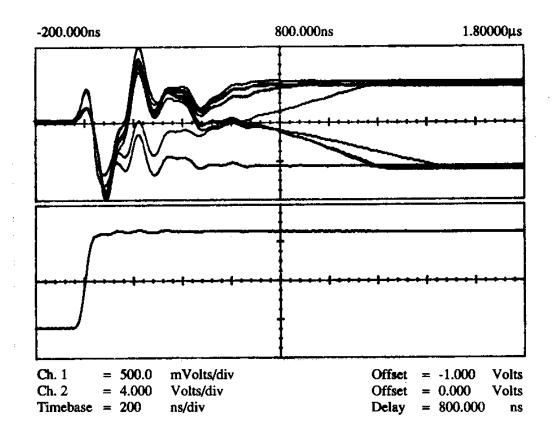

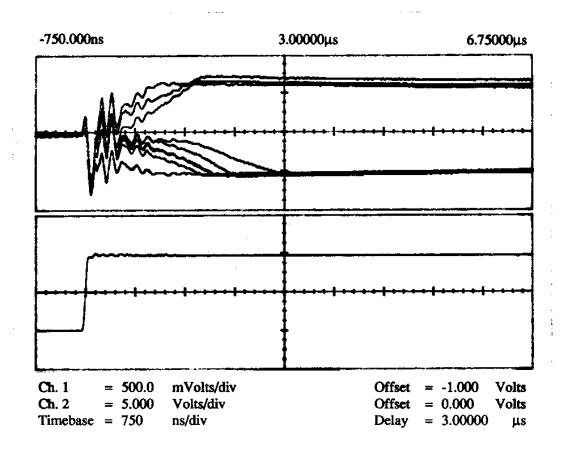

| 272   | ADA Transition from Level '0' to Level '4'; Top Trace Is Input $(500mV/div)$ , Bottom Trace Is Output $(200mV/div)$ , Offset Is $-800mV$ ; Time Scale Is $200ns/div$               | 297 |

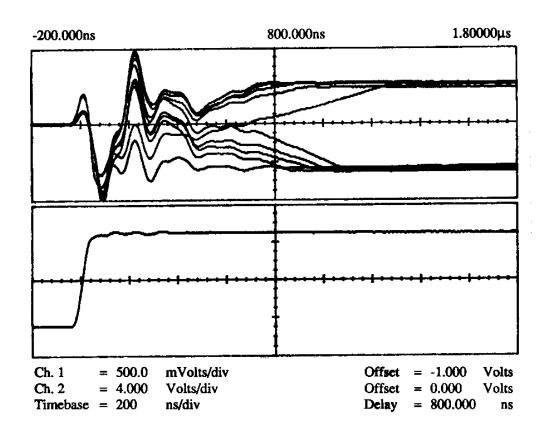

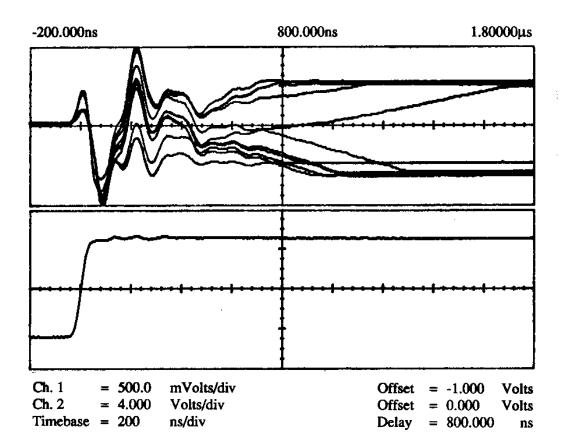

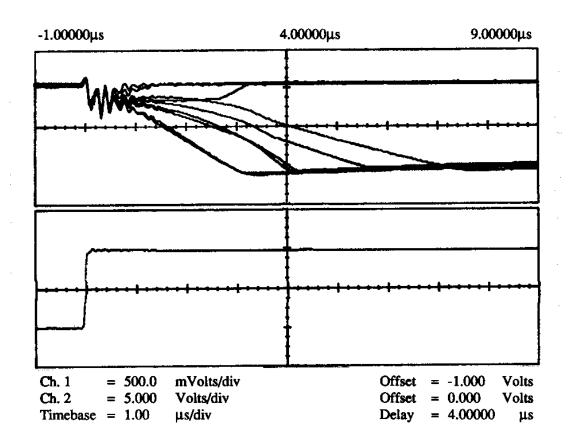

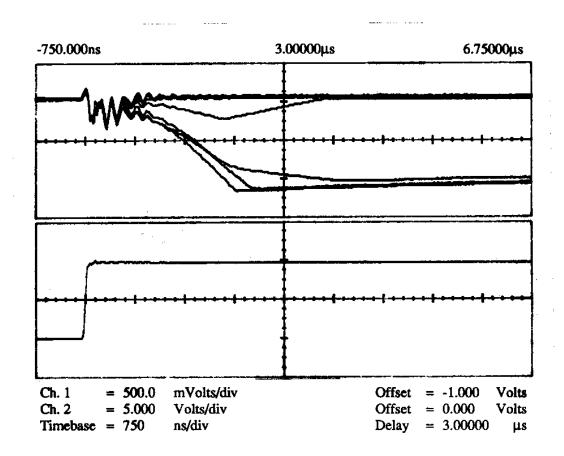

| 273   | ADA Transition from Level '0' to Level '5'; Top Trace Is Input $(500mV/div)$ , Bottom Trace Is Output $(200mV/div)$ , Offset Is $-800mV$ ; Time Scale Is $200ns/div$               | 298 |

| 274   | ADA Transition from Level '0' to Level '6'; Top Trace Is Input $(500mV/div)$ , Bottom Trace Is Output $(200mV/div)$ , Offset Is $-800mV$ ; Time Scale Is $200ms/div$               | 299 |

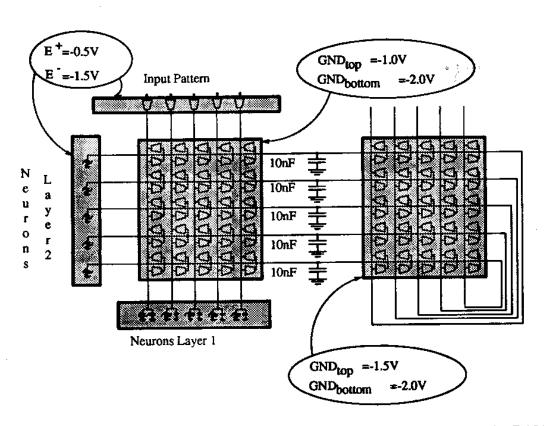

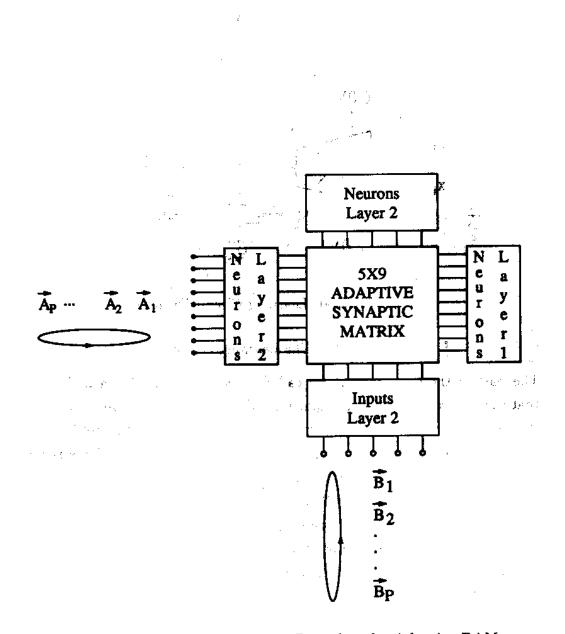

| 275   | Schematic Illustration of $5 \times 9$ Adaptive Synapse Matrix Chip                                                                                                                | 299 |

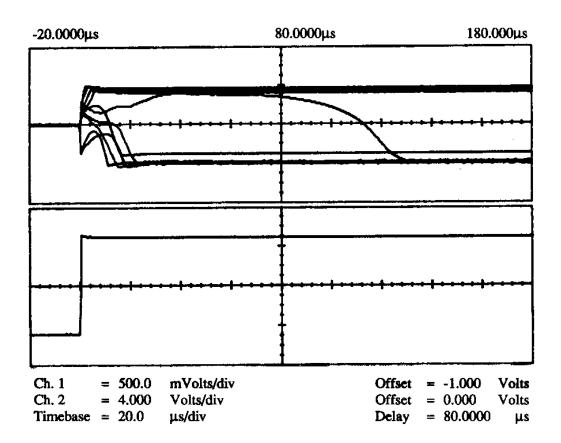

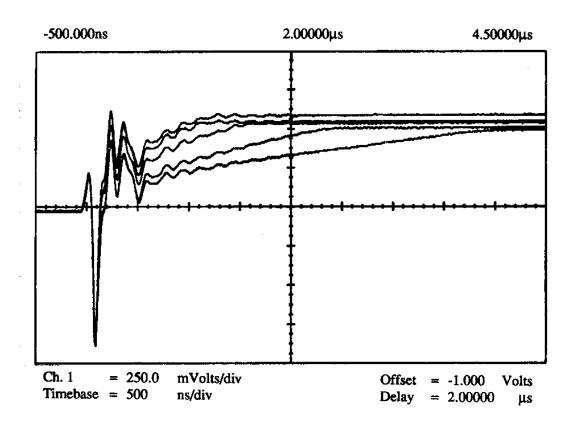

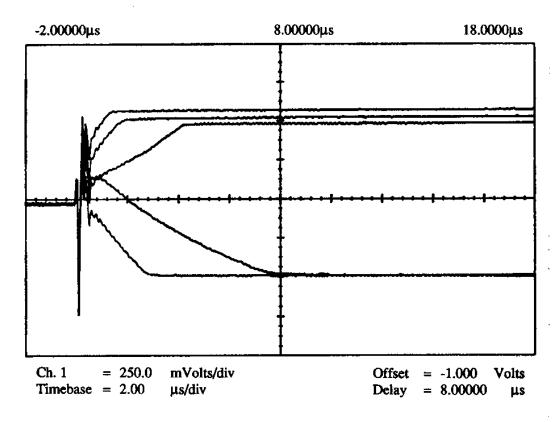

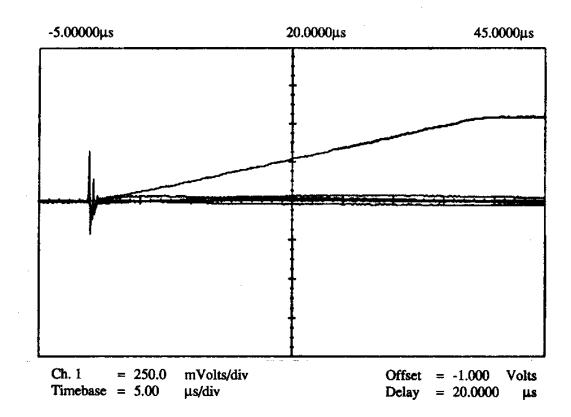

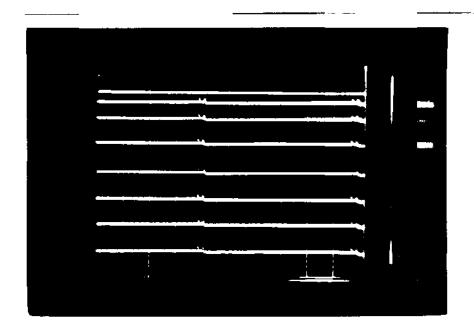

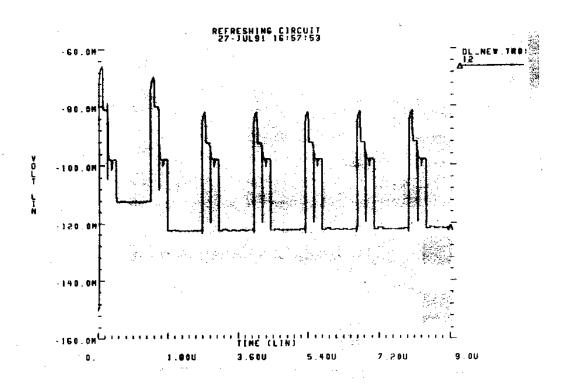

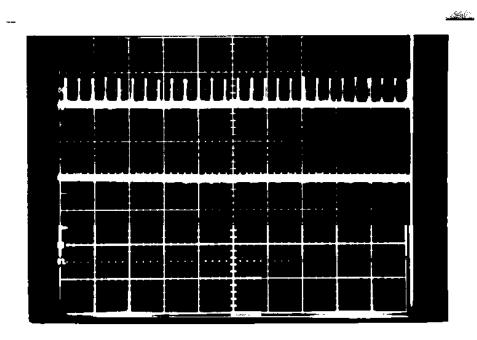

| 276   | Experimental Performance of Refreshing Circuit; Time Scale Is $5mV/div$ , Scale for Top Trace Is $10V/div$ , Scale for the Seven Bottom Traces Is $200mV/div$ with Offset $-1.00V$ | 300 |

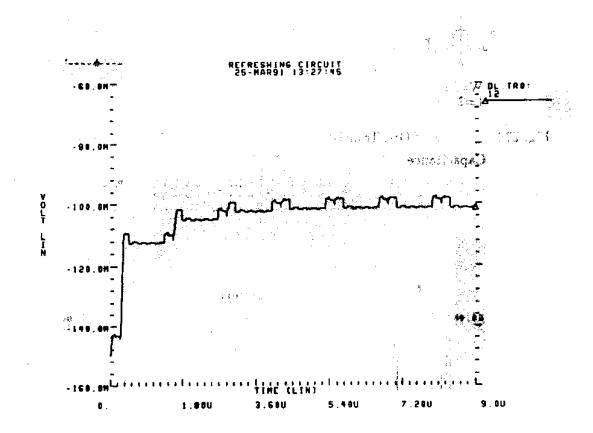

| 277   | Regular Spice Simulation of Refreshing Circuit                                                                                                                                     | 301 |

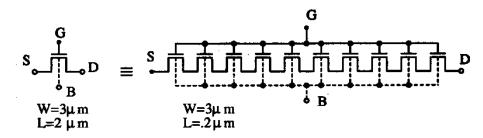

| 278   | Splitting of One Transistor into Ten to Better Model Its Distributed Channel Capacitance                                                                                           | 302 |

| FIGURE |                                                                                                                                                                                                         | Page          |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 279    | Spice Simulation of Refreshing Circuit When Splitting Transistors  M1 and M3                                                                                                                            | . 302         |

| 280    | Learning Circuit Diagram                                                                                                                                                                                | . 303         |

| 281    | Illustration of Training Procedure for Adaptive BAM                                                                                                                                                     | . 304         |

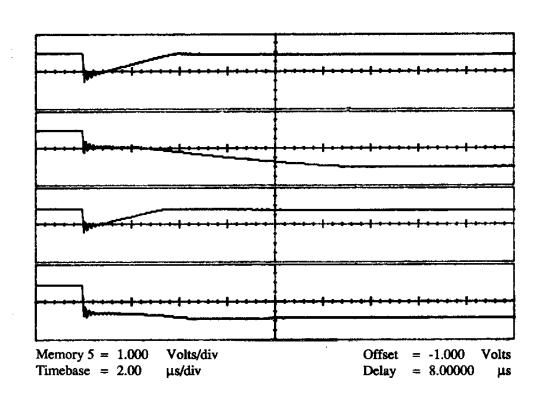

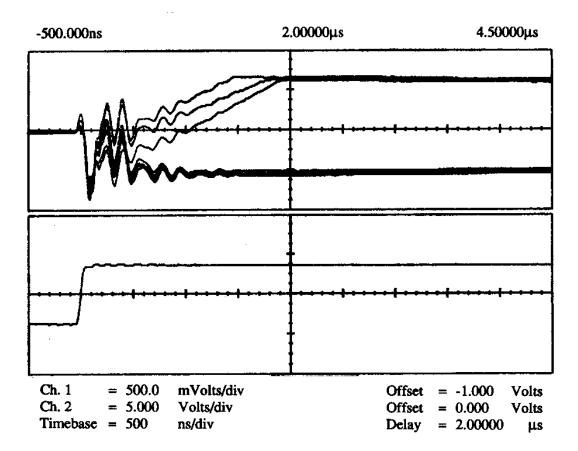

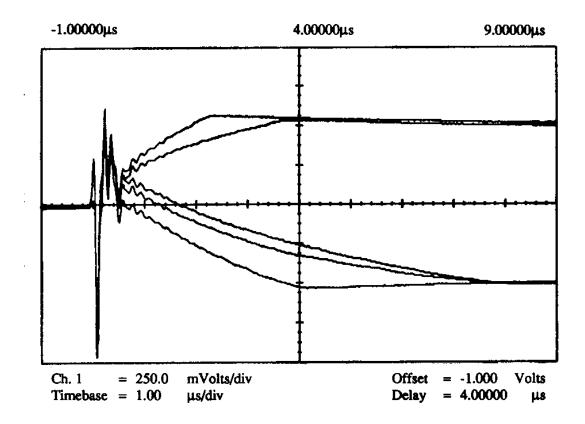

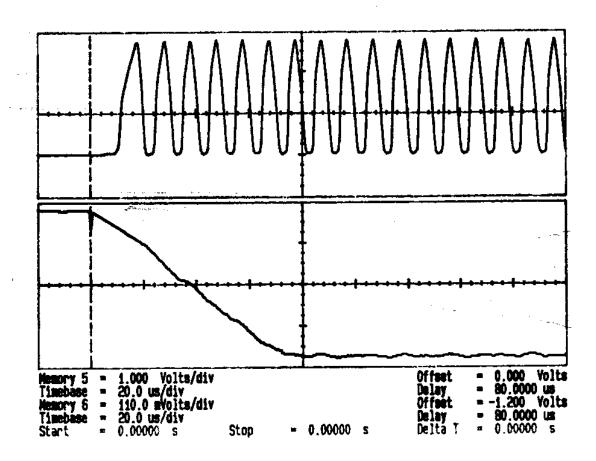

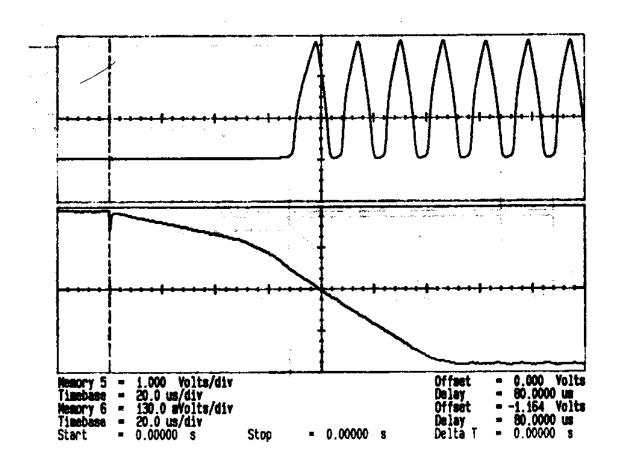

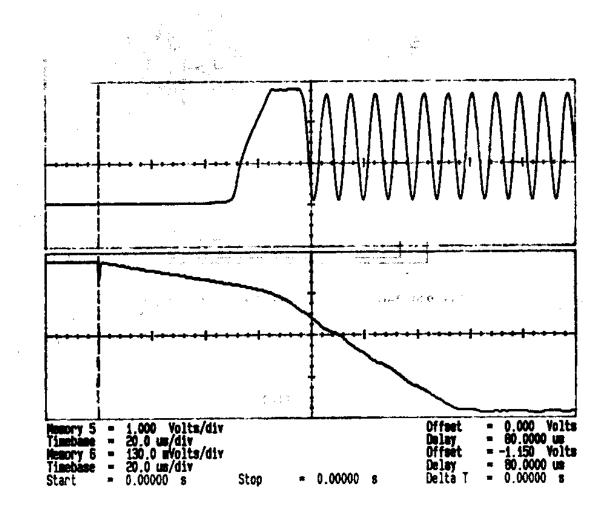

| 282    | Learning Circuit with $10KHz$ , 50% Duty Cycle Training Signal; Time Scale Is $20\mu V/div$ , Top Trace Scale Is $5V/div$ , Bottom Trace Scale and Offset Are $0.5V/div$ and $-0.5V$ , Respectively     | . 305         |

| 283    | Learning Circuit with $100KHz$ , 50% Duty Cycle Training Signal; Time Scale Is $20\mu V/div$ , Top Trace Scale Is $5V/div$ , Bottom Trace Scale and Offset Are $0.5V/div$ and $-0.5V$ , Respectively    | . 306         |

| 284    | Learning Circuit with $500KHz$ , $50\%$ Duty Cycle Training Signal; Time Scale Is $20\mu V/div$ , Top Trace Scale Is $5V/div$ , Bottom Trace Scale and Offset Are $0.5V/div$ and $-0.5V$ , Respectively | . 307         |

| 285    | Learning Circuit with $500KHz$ , 1% Duty Cycle Training Signal; Time Scale Is $20\mu V/div$ , Top Trace Scale Is $5V/div$ , Bottom Trace Scale and Offset Are $0.5V/div$ and $-0.5V$ , Respectively     | . 308         |

| 286    | Learning Circuit with $500KHz$ , 25% Duty Cycle Training Signal; Time Scale Is $20\mu V/div$ , Top Trace Scale Is $5V/div$ , Bottom Trace Scale and Offset Are $0.5V/div$ and $-0.5V$ , Respectively    | . 309         |

| 287    | Learning Circuit with $500KHz$ , 75% Duty Cycle Training Signal; Time Scale Is $20\mu V/div$ , Top Trace Scale Is $5V/div$ , Bottom Trace Scale and Offset Are $0.5V/div$ and $-0.5V$ , Respectively    | . <b>3</b> 10 |

| 288    | Learning Circuit with $500KHz$ , 99% Duty Cycle Training Signal; Time Scale Is $20\mu V/div$ , Top Trace Scale Is $5V/div$ , Bottom Trace Scale and Offset Are $0.5V/div$ and $-0.5V$ , Respectively    | . 311         |

| 289    | Single Pattern to Be Stored in the Adaptive BAM                                                                                                                                                         | . 311         |

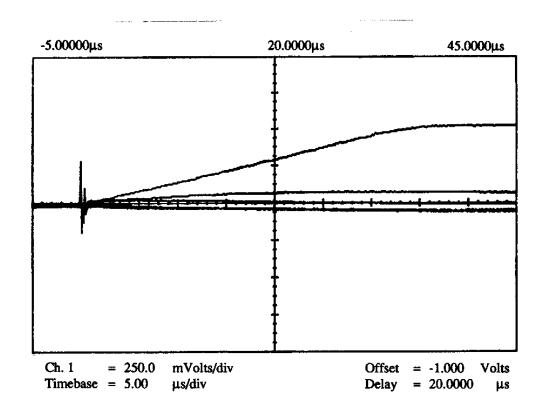

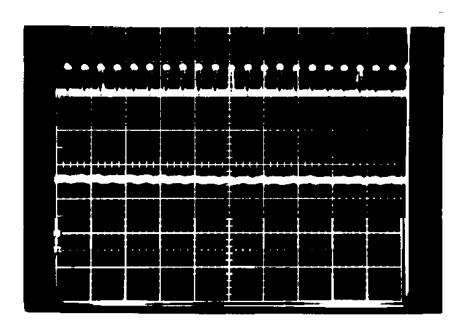

| 290    | Convergence to Pattern A with 1 Stored Pattern; Top Trace Is Trigger Signal (10V/div), Bottom Traces Are Neuron Outputs $x_i$ (200 $mV/div$ , Offset $-2.00V$ ), Time Scale Is $200\mu s/div$           | . 312         |

| 291    | Two Patterns to Be Stored in the Adaptive BAM                                                                                                                                                           | . 313         |

| 292    | Convergence to Pattern A with 2 Stored Patterns; Top Trace Is Trigger Signal (10V/div), Bottom Traces Are Neuron Outputs $x_i$ (200 $mV/div$ , Offset $-2.00V$ ), Time Scale Is $200\mu s/div$          | . <b>313</b>  |

| FIGUR | E .                                                                                                                                                                                              | Page  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 293   | Convergence to Pattern $B$ with 2 Stored Patterns; Top Trace Is Trigger Signal (10V/div), Bottom Traces Are Neuron Outputs $x_i$ (200 $mV/div$ , Offset $-2.00V$ ), Time Scale Is $200\mu s/div$ | . 314 |

#### CHAPTER I

#### INTRODUCTION AND BACKGROUND

"In 1987 the American Institute of Electrical and Electronic Engineers (IEEE) called the first conference on neural networks. It took place in San Diego, California, where 200 authors presented their papers to 2000 delegates. It was described as the dawn of a new era. The scientists were talking of a kind of computing that is inspired by the cellular networks of living brains. The following year we saw even bigger events: more papers and more delegates. So, as far as most computer scientists were concerned, something new was going on" [1].

What is happening? New systems are being proposed, built and studied that are based on a type of computing different from the conventional one proposed by Von Neumann [2] and that resembles living brains. The classical approach consists of executing a step by step algorithm developed by one or more persons who tried to represent their way of solving a certain problem into a computational procedure. In the new approach the system learns from its own experience, like humans do. When a little child is taught that a certain object is called table, nobody gives him or her a sequence of instructions that say something like If 1) it has a horizontal platform, 2) is elevated from the ground by one or more legs, and 3) you can put things on it, then this is a "table". The way the child is taught is by showing him or her a table. The more tables one shows to the child the more general and abstract is the idea he or she develops about the concept table.

The basic idea behind the area of study called connectionism, neural networks, or parallel processing (all of these names are synonyms) is that of systems having a structure that, at some level, reflects what is known of the structure of the brain. Such systems are characterized by the fact that they can be taught through examples (like humans), instead of being programmed.

However, in artificial as well as in natural neural network systems we can distinguish between two big categories,

Inherently Nonlearning Neural Networks. These networks do not change or adapt to the flux of external signals coming from the surrounding environment.

These systems (or subsystems) are used to perform preprocessing of sensory signals in order to generate other signals more suitable for the next processing stages. Examples are the layers of neurons found in the retinas and cochleas of living beings that transform visual and auditory signals into nerve impulses that go to the brain. They also can perform some elementary signal processing tasks such as automatic gain control, noise suppression, contrast enhancement, motion detection, ...<sup>1</sup>. Neural networks that are inherently nonlearning are characterized by the fact that the value of a weight does not depend on the neurons it interconnects.

• Inherently Learning Neural Networks. These networks do adapt to the flux of external signals coming from the surrounding environment. They are responsible for the intelligent type tasks such as pattern recognition, associative memory, pattern clustering and classification, optimization, . . . . Neural networks that are inherently learning are characterized by the fact that the value of a weight does depend on the neurons it interconnects.

Note that when an inherently learning neural network algorithm is implemented in hardware it can be made with fixed, programmable or adaptive weights.

In this Dissertation we are interested in the hardware implementations of inherently learning neural network systems. However, we will describe briefly in this Chapter some of the work reported on inherently nonlearning neural systems. Most of this work is done in hardware (instead of software) because it deals directly with the transformation of real world signals. On the other hand, the so far reported work on Inherently Learning Neural Networks has been done mostly in software. It is usually studied by mathematicians or computer scientists who develop special software for "conventional" computers. In this Chapter we will also present some of the neural networks of this type. Later on, in further Chapters, we will introduce a modular circuit design technique that will allow us to implement in hardware most of the architectures reported on neural networks. This technique is able to implement in hardware a set of nonlinear continuous time differential equations that characterizes most of the reported architectures. However, many of these architectures have been reported as described by a set of discrete time difference equations. But according to

<sup>&</sup>lt;sup>1</sup>In living beings these neural subsystems might be subject to some adaptation during the early stages of life.

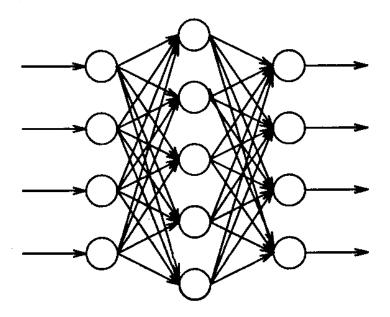

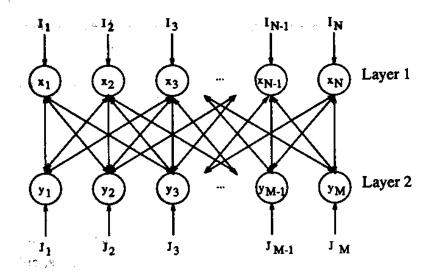

Fig. 1. General Neural Network Concept

Grossberg [3] there is always a mapping<sup>2</sup> between the discrete time neural system and the continuous time one. Therefore, our hardware circuit design technique can also be used to realize the discrete time systems, provided they are previously mapped into a continuous time system.

### A. The General Neural Network Concept

The general concept of a neural network is illustrated in Fig. 1. It is formed by a set of processing elements called neurons interconnected in a certain fashion, some of them receiving the external inputs, and some of them generating the system output signals. Each neuron receives signals from other neurons and might receive also some external signals. It processes all these inputs and generates an output that will be sent to other neurons and/or to the output of the system. The interconnection between two neurons, say neurons i and j, is called synapse and is characterized by the weight or strength  $w_{ij}$  of this interconnection. The set of weights of the system  $\{w_{ij}\}$  characterizes its input-output behavior. This set of weights can be preprogrammed into the system to make it perform a certain task. The set of weights can also be made to change during the life of the neural system depending on the input signals it receives and/or the output signals it generates. This occurs in neural networks with learning (or adaptive) that change their behavior according to the input signals they receive from the surrounding environment.

<sup>&</sup>lt;sup>2</sup>Which is shown in equation (1.7).

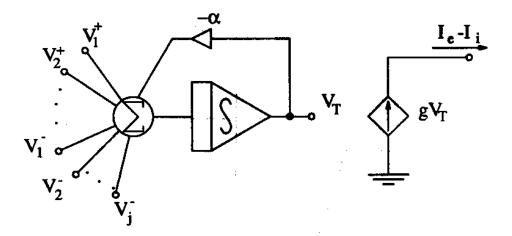

Fig. 2. General Interconnection Topology for One Neuron

Mathematically, and with reference to Fig. 2, we can consider for each neuron the following. Assume  $x_j$  is the output signal generated by neuron j. Neuron j is receiving the outputs from neurons 1 to n, plus an external signal  $I_j$ . The interconnections between two neurons, say neurons i and j, is characterized by the weight of the synapse  $w_{ji}$ . Each synapse generates a signal  $F_{ji} = F_{ji}(x_i, w_{ji})$  that will be one of the inputs to neuron j. Neuron j receives all these signals and after processing them generates its output signal,

$$x_{i} = G_{i}(F_{j1}, \dots F_{ji}, \dots F_{jn}, F_{jq})$$

(1.1)

The function  $G_j(\cdot)$  performs some kind of nonlinear processing. Generally it is made the same for all neurons and is defined as a function of the sum of all the inputs,

$$G_i(F_{j1}, \ldots F_{ji}, \ldots F_{jn}, F_{jq}) = G(F_{j1} + \ldots F_{ji} + \ldots F_{jn} + F_{jq})$$

(1.2)

and each of these inputs takes the particular form of a product,

$$F_{ji}(x_i, w_{ji}) = w_{ji}x_i, \quad i = 1, \dots n$$

$$F_{jq}(I_j, w_{jq}) = w_{jq}I_j$$

(1.3)

Once the neuron receives all the inputs, its dynamic is usually described in two ways: