# iCaveats —a Project on the Integration of Architectures and Components for Embedded Vision

- R. Carmona-Galán

- J. Fernández-Berni

- A. Rodríguez-Vázquez

P. López V. Brea

D. Cabello

- G. Domenech-Asensi

- R. Ruiz-Merino

- J. Zapata-Pérez

## Abstract

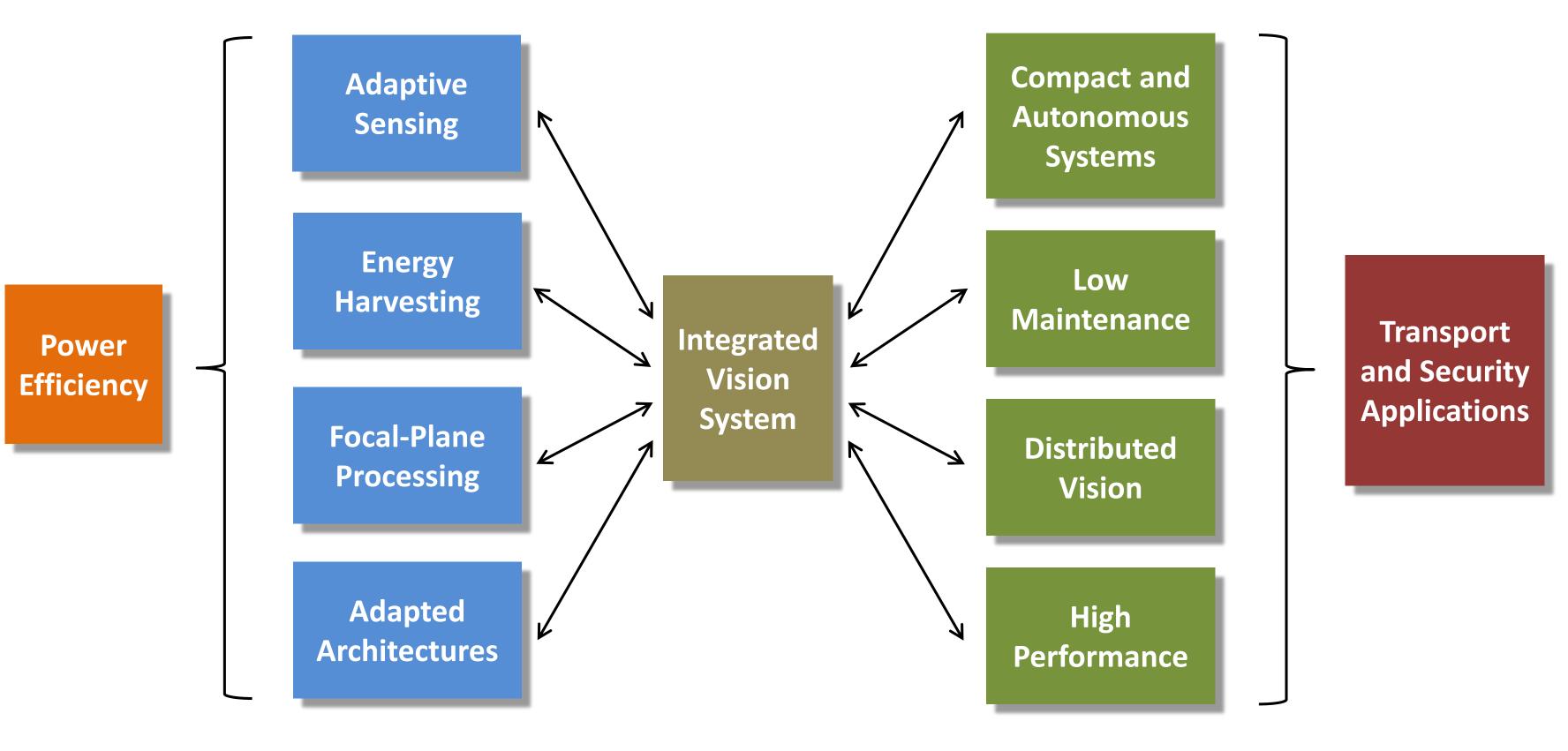

The visual stimulus contains a great deal of data, demanding a considerable computational effort to be processed and interpreted. Compact and low-power implementation of an autonomous vision system is not easy to accomplish. Efficiency can be achieved by

distributed resources and relatively coarse processing blocks. The main mixed-signal problem of this approach is the lack of flexibility to be migrated to other application fields. The objective of project iCaveats is developing a library of hardware components

and architectures that would be transparent to the application developer. We have worked in hardware acceleration of image processing capabilities, energy sensor management and sensory chip interfacing.

## Initial hypothesis

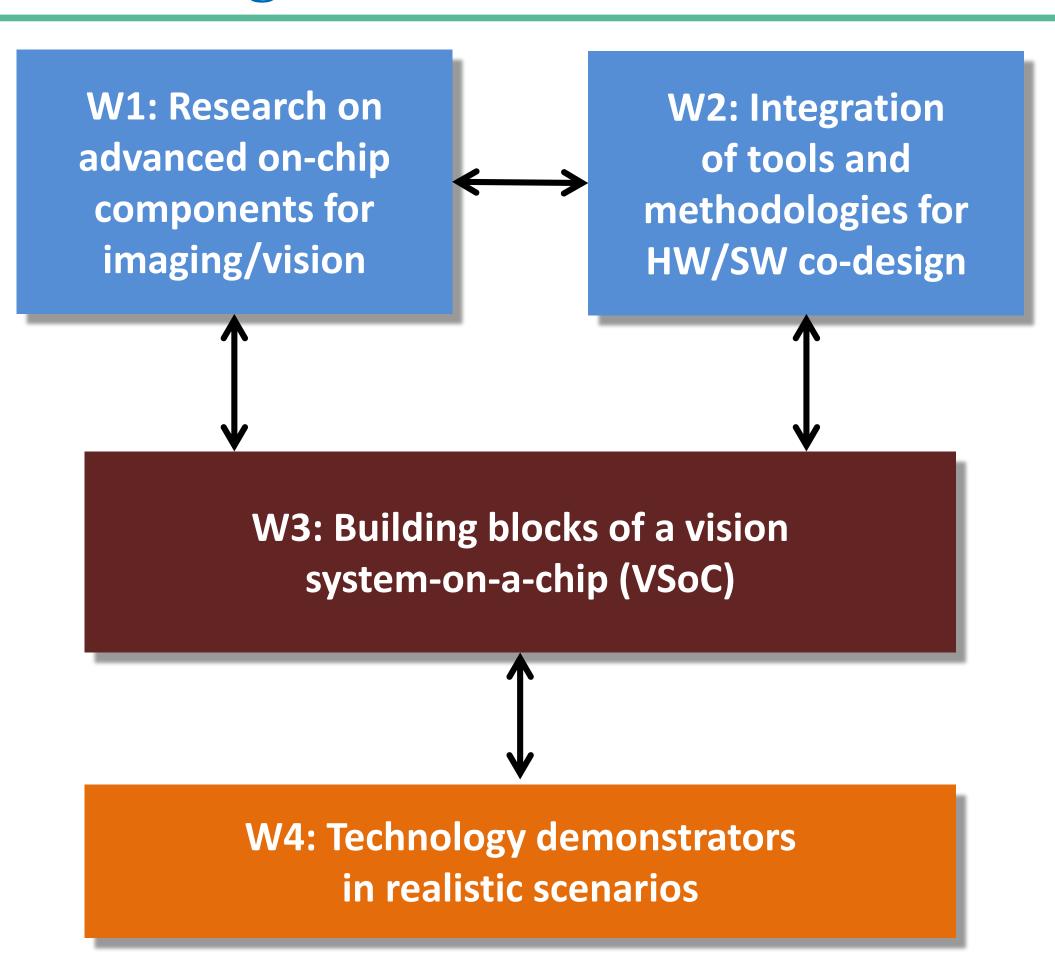

## PERT diagram

## Project results

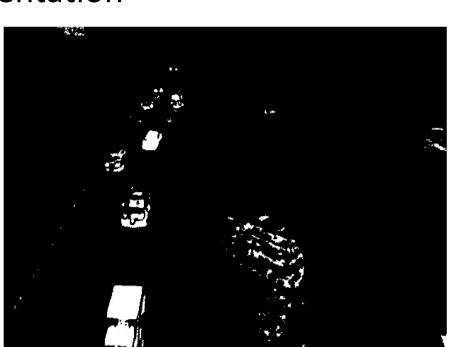

#### **HW-Oriented Pixel-Based Adaptive Segmenter**

- Evaluation of hardware non-idealities

- In-sensor foreground segmentation

SPAD camera prototype

64×64px SPAD imager

Min. illumination 160uW

XEM3010 FPGA board

PDE 5% @640nm

Resolution 1cm

• 1.1 kfps

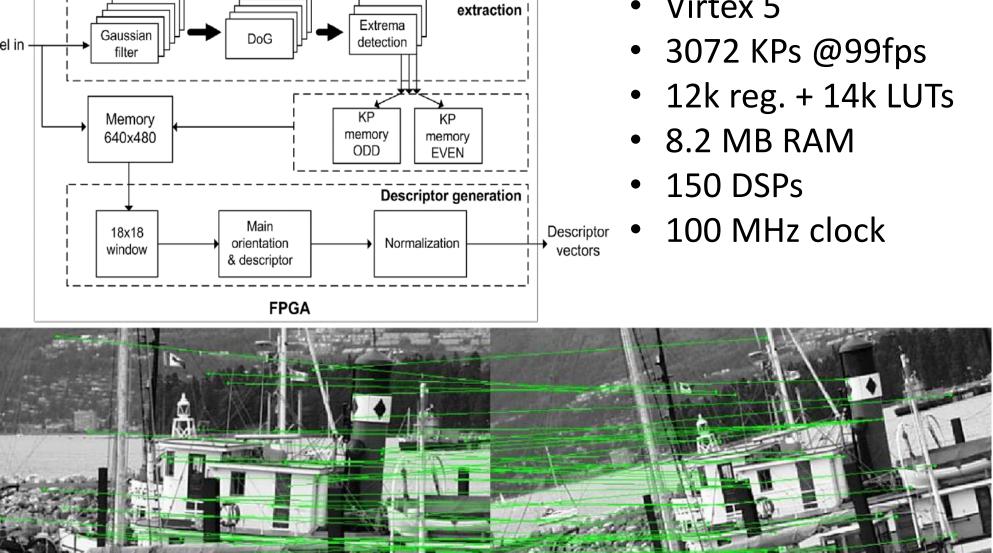

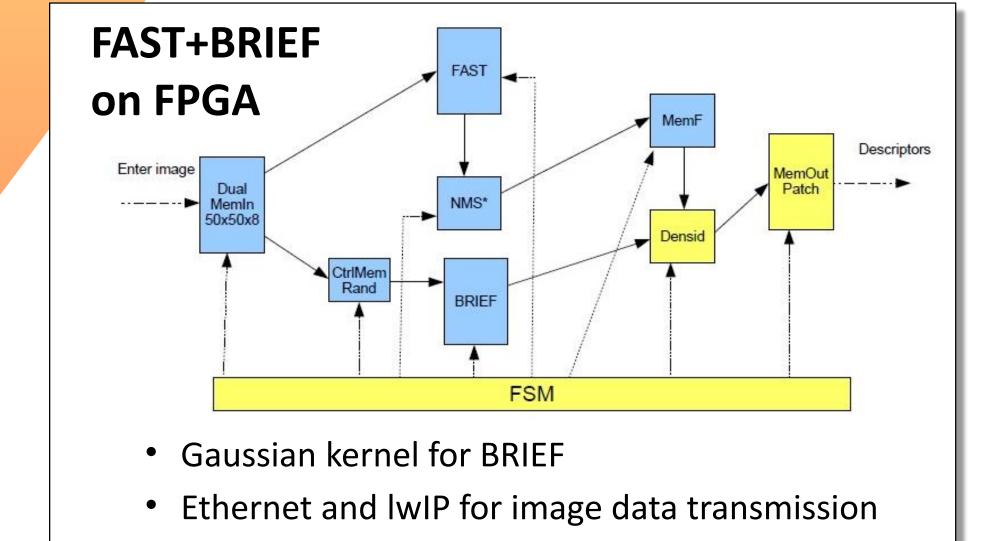

#### All-hardware SIFT implementation

Virtex 5

Real-time DNN inference in Raspberry-Pi

Caffe

SqueezeNet

• 58.6 ms/frame

• 17.16 fps

• 3.07-3.90 W

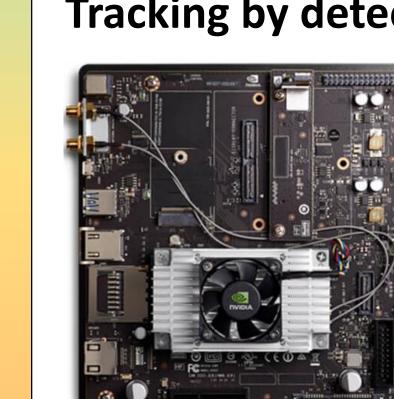

## Tracking by detection on Jetson TX2 NVIDIA embedded

computer for Al

Neural Computing Stick

2.83 matches/J (top-1)

- HO-PBAS + GOTURN

- Adapted for multiple object detection and tracking

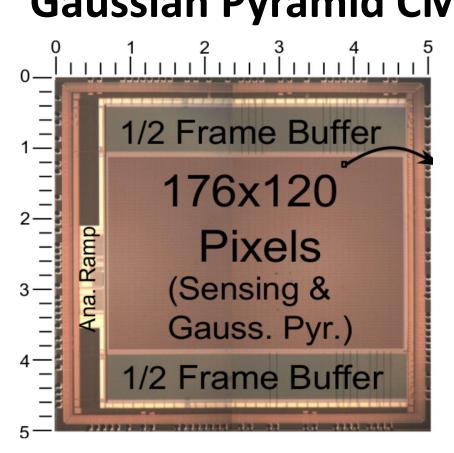

## **Gaussian Pyramid CMOS vision sensor**

- 0.18µm CMOS technology

- Power: 70mW

- Frame rate: 125 fps

- 26.5 nJ/px @ 2.64 Mpx/s

## 3D-integrable architecture

Reduced data flow

- Latency < 5ms

- Accuracy

- 0.05° (φ)

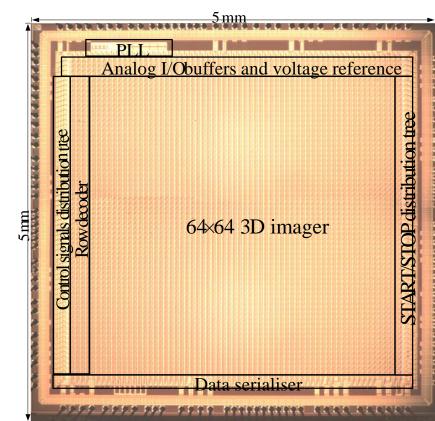

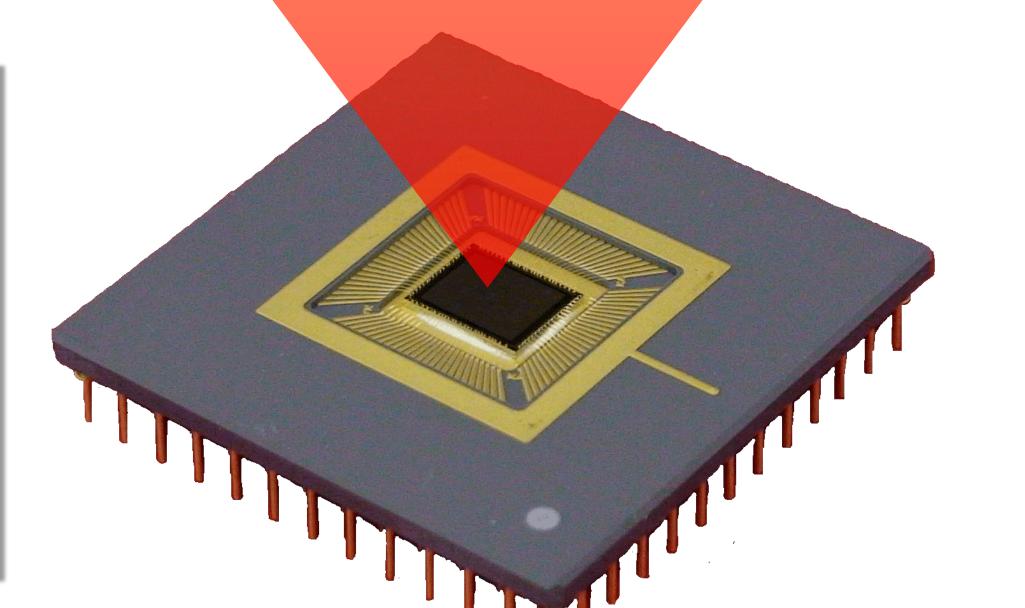

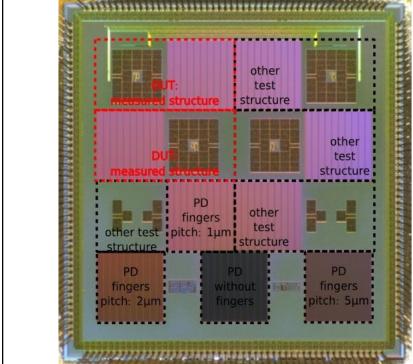

### **CMOS-SPAD 3D Imager**

- 0.18µm CMOS technology

- < 290ps total jitter

- 11b resolution

- SPAD power < 10mW

- Frame rate:

- - 1kfps complete image 100kfps interframes

### Sun sensor for satellite navigation

- Dynamic range > 100dB

- Resolution 0.03°

- $0.0132^{\circ} (\theta)$

## **CMOS** ambient-light energy harvester

Descriptor + corner detector

- 0.18µm CMOS technology

- 1.575 mm<sup>2</sup> die size

- 1 mm<sup>2</sup> solar cell

- Efficiency:

- 25% low inputs

- 40% high inputs