Trabajo de Fin de Máster "Máster Universitario en Microelectrónica: Diseño y Aplicaciones de Sistemas Micro/Nanométricos"

# Octopus image sensor with asynchronous windowed readout

Escrito por Sergio Palomeque Mangut Dirigido por Juan Antonio Leñero Bardallo 3 de julio de 2023

### Acknowledgments

Para mí madre, para mí padre.

Quiero agradecer al profesor Juan Antonio Leñero Bardallo la supervisión de este trabajo. Juan Antonio generosamente me dió la oportunidad de incorporarme a su equipo de investigación en el IMSE, donde trabajo con comodidad en una línea que me está apasionando. Espero poder seguir investigando junto a él en sensores de imagen basados en eventos durante muchos años venideros.

Este trabajo ha sido posible gracias a mis compañeros del IMSE. Ellos sostienen la actividad del centro, muchas veces sin el reconocimiento que merecen. Gracias a Pablo, a Valentín, a Rubén, a Carlos 'Senior', a Roberto, a Rafa, a Carlos 'Junior', a Iván, a Laura y a Javi.

Y a mi hermano, David. Mi vida es más fácil porque sigo sus pasos.

ii

## Contents

| Acknowledgements                                                                                                                                                                                                          | i                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| List of Figures                                                                                                                                                                                                           | ix                                                    |

| List of Tables                                                                                                                                                                                                            | xi                                                    |

| Abstract, Motivation and Objectives                                                                                                                                                                                       | xiii                                                  |

| Abstract, Motivations and Objectives                                                                                                                                                                                      | xiii                                                  |

| 1 Fundamentals of Octopus Image Sensors         1.1 Introduction         1.2 Event-based image sensors         1.2.1 Octopus sensor         1.2.2 Address event representation (AER)                                      | · · 2<br>· · 6                                        |

| 2 Asynchronous Readout         2.1 Tenderness towards synchronous readout techniques         2.2 Arbiters         2.2.1 Greedy arbiter         2.2.2 Fair arbiter         2.3 Our solution: windowed asynchronous readout | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| <ul> <li>3 Octopus Pixel</li> <li>3.1 Introduction</li></ul>                                                                                                                                                              | $\begin{array}{cccccccccccccccccccccccccccccccccccc$  |

| 4 AER Periphery         4.1 Sender interface         4.2 Encoders         4.3 Arbiter tree                                                                                                                                | 49                                                    |

| 5 Expected Results and Future Work                                                                                                                                                                                        | 55                                                    |

| Bibliography                                                                                                                                                                                                              | 57                                                    |

# List of Figures

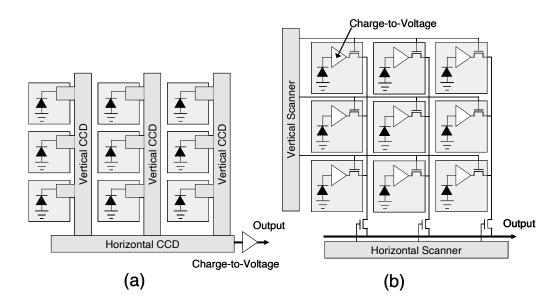

| 1.1 | Comparison between CCD and CMOS image sensors [5]. (a) CCDs transfer simul-<br>taneously the signal charges of its photoreceptor, as received, to the next CCD. A<br>fast shift register at the end of the lines sends them to an amplifier for external read-<br>out. (b) A CIS uses amplification in each pixel, converting the signal charge into a<br>voltage signal . Although CIS were more sensible to fixed-pattern noise (FPN), this<br>drawback has been eliminated.                                | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

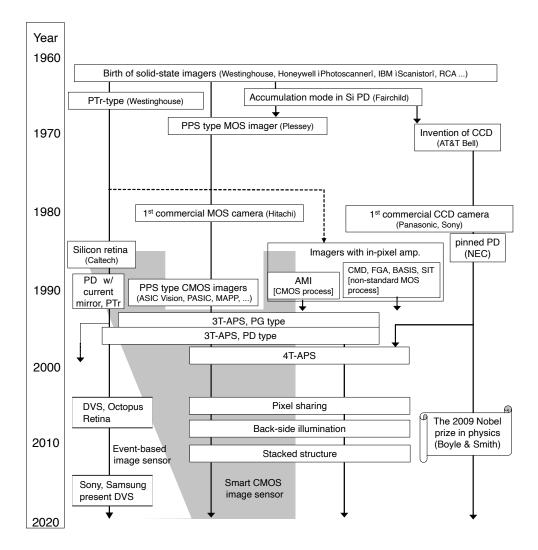

| 1.2 | Historical evolution of digital image sensors. Originally from [5], modified in this work                                                                                                                                                                                                                                                                                                                                                                                                                     | 3  |

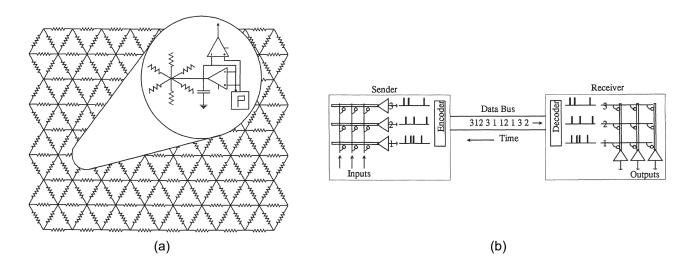

| 1.3 | Silicon retina designed by Mahowald [16]. (a) Diagram of the silicon retina showing the resistive network and a single pixel element. (b) Address event representation (AER) scheme. Asynchronous neurons request control of the bus when they generate action potentials and transmit their addresses.                                                                                                                                                                                                       | 4  |

| 1.4 | Preliminary image deblurring results on high-speed scene, obtained combining Prophesee Metavision sensor and algorithms with Snapdragon platform.                                                                                                                                                                                                                                                                                                                                                             | 5  |

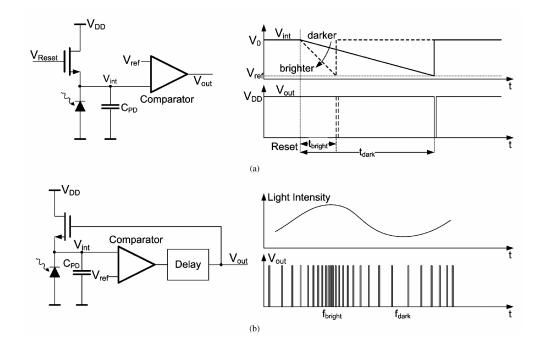

| 1.5 | Pulse-modulation imagers [28] These pixels transmit absolute intensity of incident<br>light through the timing of events in the comparator's output. (a) Time-to-first<br>spike (TTFS) architecture, based on PWM. Brighter pixels spike sooner than darker<br>pixels. (b) Octopus pixel architecture, using PFM encoding. Larger photocurrents<br>are converted into higher frequencies                                                                                                                      | 7  |

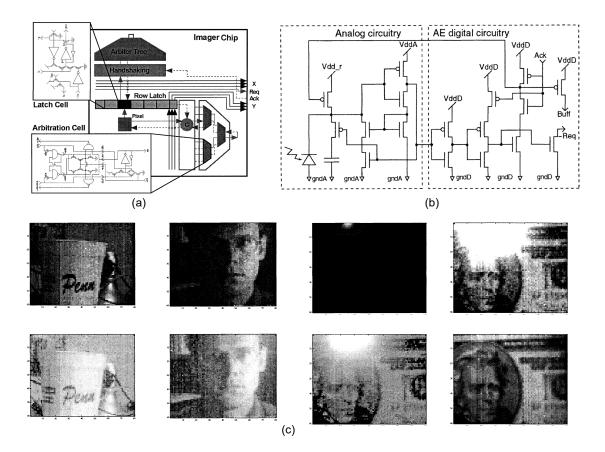

| 1.6 | Schematics and images from the original octopus sensor [29]. (a) Asynchronous AER readout. A latch buffers the request from the pixel. The request signals are arbitered in the arbiter trees, which select the first pixel that produced an event. The encoders output the address of that selected pixel. (b) Pixel schematic, showing the current-feedback event generator and the in-pixel handshake circuit. (c) Example images with linear intensity (top) and log scale (bottom).                      | 8  |

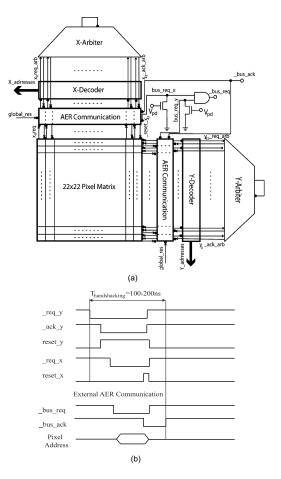

| 1.7 | <ul> <li>(a) Schematics of an octopus sensor as an AER sender implemented by Leñero [34]. The first stage provides buffering and signal control for requests and acknowledges pixel arbitration. Requests are sent to an arbiter tree, which selects the winning row or column through an acknowledge, which then selects a word from the encoder.</li> <li>(b) Signal flow of the arbitration between rows and columns, and the AER point-to-point link with a 4-phase handshaking protocol [38].</li> </ul> | 10 |

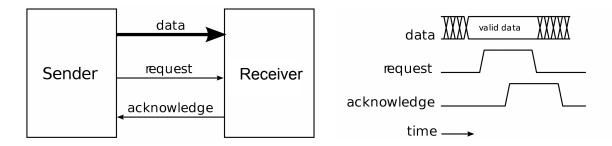

| 2.1 | (Left) A 4-phase, bundled-data communication. A sender is connected to a receiver<br>by data lines, a request line, and an acknowledge line. (Right) Its timing diagram.<br>When the request line is low, the data is to be considered invalid and liable to change<br>at any time. The sender usually waits for the acknowledge signal to remove the data<br>from the data bus.                                                                                                                              | 14 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

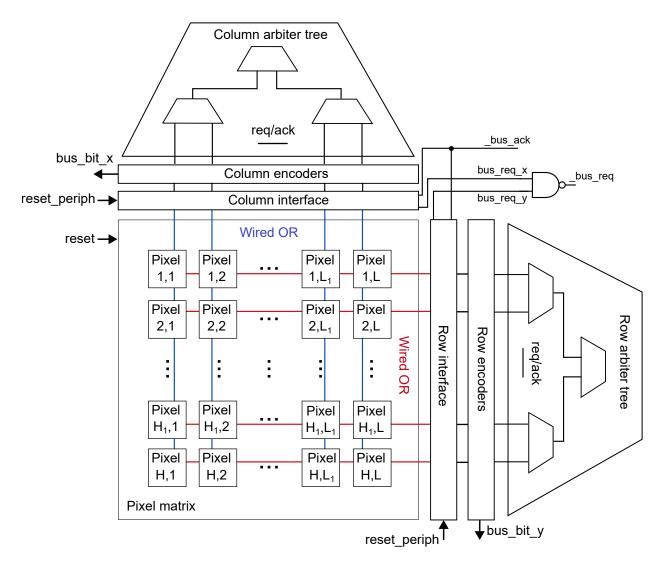

| 2.2 | Block diagram of an asynchronous readout AER implementation for an event-based image sensor with a resolution of L x H pixels in a grid arrangement. The row and column interface can include pull-up elements for the wired ORs, buffers, and latches, as well as control logic for handshake signals. The main limitation we face when scaling pixel count is the size of the wired ORs. These column and row metal lines get longer and have more pull-down transistors connected to them, causing the capacitance of the lines to increase, degrading signal integrity and slowing the readout process. In the arbiter trees, each line is actually formed by two wires: a request and an acknowledge. There are $\ln(L)$ (or $\ln(H)$ ) levels and L - 1 (or H - 1) arbiters in each tree, in the case of square matrix dimensions                                                                                                                                                            | 15 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

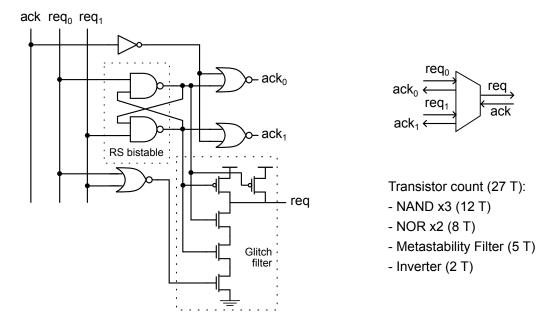

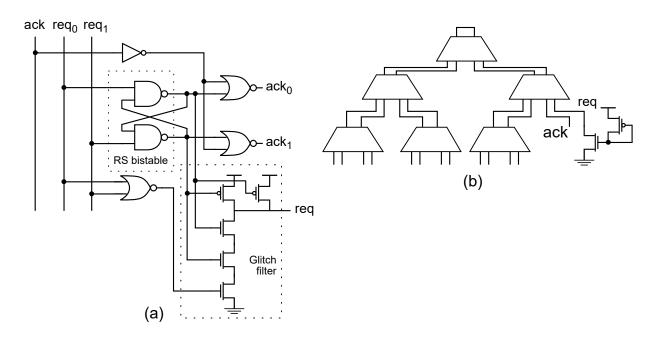

| 2.3 | Circuit implementation of a glitch free 2-way greedy arbiter [49]. The RS bistable $(req_0 = S, req_1 = R)$ and metastability filter form the core mutual exclusion element. It exclusively acknowledges one of two incoming requests, only if its own outgoing request is acknowledged. The glitch filter prevents a condition where the output request switches logic briefly. The transistor count is 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16 |

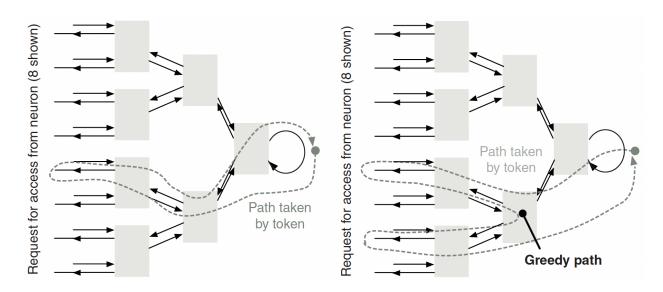

| 2.4 | Token movement in an arbiter tree to handle the requests from neurons. In a greedy<br>arbiter tree, neurons located near each other may form a greedy path because the<br>token does not need to reach to the top of the tree. A fair mechanism is needed to<br>ensure that requests from an arbiter are blocked until its parent's acknowledge is<br>cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17 |

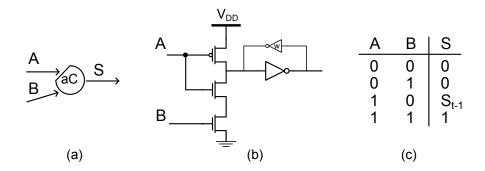

| 2.5 | Asymmetric Muller C-element, an essential component for understanding the fair arbiter behavior. (a) Symbol of the circuit. (b) Transistor implementation. (c) Truth table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18 |

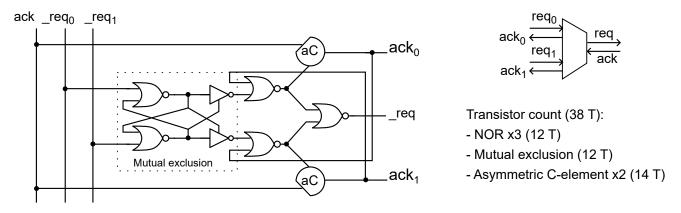

| 2.6 | Asynchronous fair arbiter implemented by Fok and Boahen [47]. The RS bistable<br>with NOR gates implies the use of active-low logic for requests. A metastability<br>filter is implemented with two inverters at the output of the latch, with pull-down<br>source connected to the reciprocal request. The asymmetric C-element guarantees<br>that no greedy path is created. Transistor count is higher than for the greedy arbiter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18 |

| 2.7 | Image artifact occurs by the mismatch between event generation time and readout time for high event rates [51]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18 |

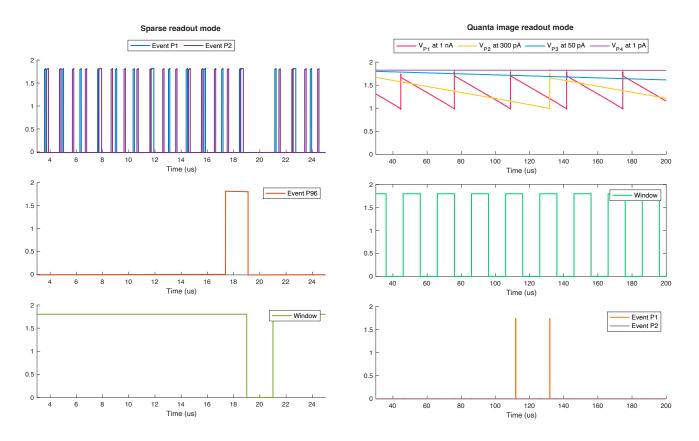

| 2.8 | The two readout modes proposed in this work. The octopus sensor we designed<br>implements a switch to decouple event generation from transmission through a signal<br>called Window. (Left) The sparse readout mode is based on the works of Karen<br>Adam [53], and will enable us to scan the events of those pixels in the matrix that<br>are not receiving the attention of the periphery. (Right) The quanta image mode,<br>based on the sensor conceived by Fossum [55], will use the window to randomly<br>sample the Poisson process of the spikes produced in the matrix.                                                                                                                                                                                                                                                                                                                                                                                                                 | 20 |

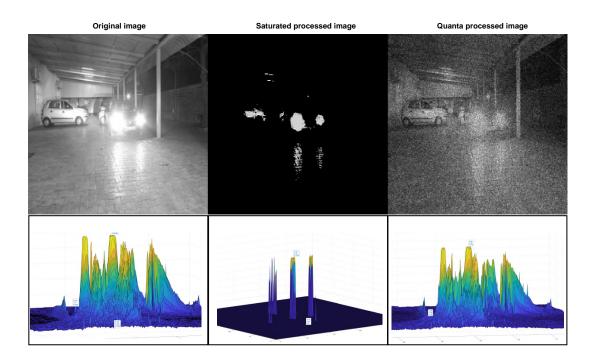

| 2.9 | Results from the Matlab models developed by Méndez-Romero [54]. In the top, an example bright image is used to evaluate the saturation in the AER channel and the impact of quanta-based acquisition. In the bottom, a 3D representation of the spikes in each pixel. In the original image, the most illuminated pixels have 55000 spikes, whereas its darker parts have around 2000. Roberto used a linear transformation that assigned spiking frequencies between the brightest and to the darkest pixel. Then, he modeled saturation by comparing the sum of all spikes in the matrix with the common saturation rate of the AER periphery. If the sum is bigger, he erased spikes of the less illuminated pixels. Last, he modeled quanta acquisition by dividing the original image in a cube of binary bit planes, each indicating whether the pixels had spiked at least once, and randomly eliminated spikes of each plane. The number of spikes is better distributed among all pixels. | 21 |

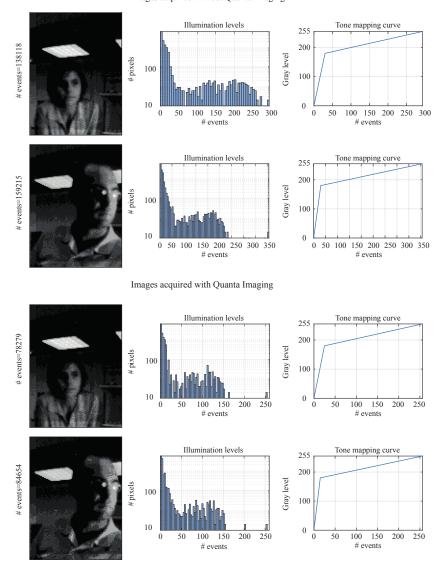

| 2.10 | Results from a quanta-based post-processing using an image adquired by an octopus sensor [55]. The original images were acquired using an octopus sensor, and are formed by around 150.000 events each. After post-processing, using a window with a uniform distribution and 0.7 average duty cycle to sample the spikes, the images are still recognizable. The result is that each image can be represented with half the events.For each one of the images, histograms and the applied tone mapping curves are shown.                                                                                                                                                         | 22 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

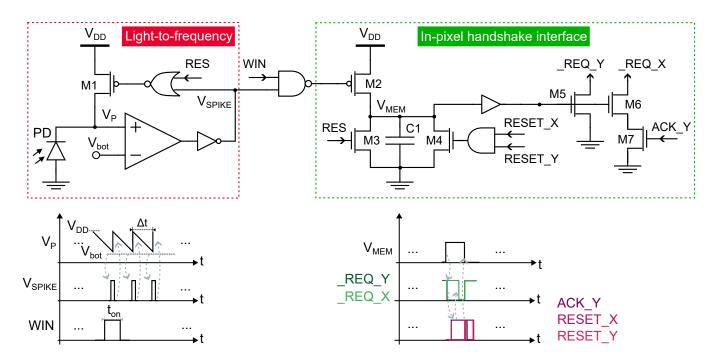

| 3.1  | Pixel schematic and signal flow [30]. The incident light is encoded in the frequency<br>of $V_{\text{SPIKE}}$ . Spikes produce a self-reset in the comparator's input. The circuit im-<br>plements an integrate-and-fire neuron model. The in-pixel handshake interface with<br>memory capacity implements the logic for arbitration between pixels and AER com-<br>munication. The window decouples spike generation from communication. Transis-<br>tor sizes (µm/µm): M1 = 0.24/0.34, M2 = 0.45/0.18, M3 = M4 = 0.24/0.18, M5 =<br>2/0.18, M6 = M7 = 1.6/0.18. Total transistor count: 37. C = 20 fF. Discharging<br>time of the capacitance due to current leakage: 336.77 µs | 24 |

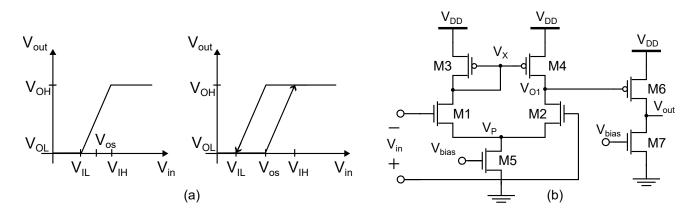

| 3.2  | (a) Transfer characteristic of a comparator considering finite static gain and offset voltage (left) and hysteresis (right). (b) We use the two-stage comparator with NMOS input. Transistor sizes ( $\mu$ m/ $\mu$ m): M1 = M2 = 0.67/1.1, M3 = M4 = 1.34/2.2, M5 = M7 = 0.37/0.48, M6 = 0.3/0.6.                                                                                                                                                                                                                                                                                                                                                                                | 25 |

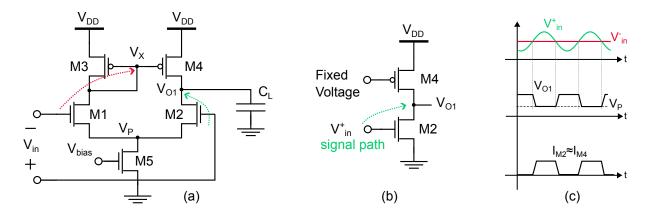

| 3.3  | (a) Large-signal analysis of the first stage of the comparator, with the two signal paths affecting the single-ended output. Note that $V_{\rm in}$ polarity respect to a 5-T OTA depiction is reversed, as the second stage of the comparator inverts the output. (b) The $V_{\rm in}^+$ signal path can be studied as a NMOS common source amplifier. (c) Influence of $V_{\rm in}$ in $V_{\rm o1}$ and in the current of the right branch.                                                                                                                                                                                                                                     | 26 |

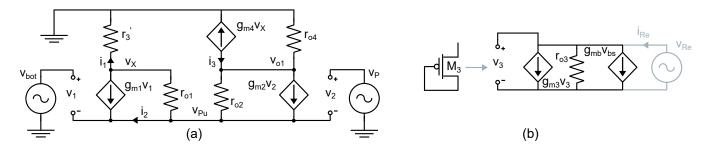

| 3.4  | (a) Small-signal circuit of the comparator's first stage. Although $V_{\text{bot}}$ is a constant DC reference, we include its AC component for the calculation procedure. (b) Small-signal equivalent of a diode-connected PMOS.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27 |

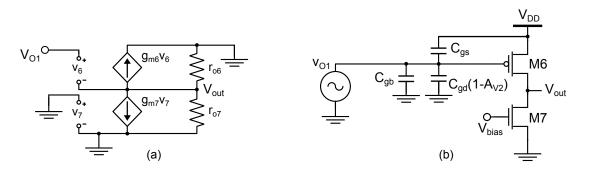

| 3.5  | (a) Small-signal equivalent circuit of the common-source amplifier. (b) High-frequency model of the stage with Miller's approximation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29 |

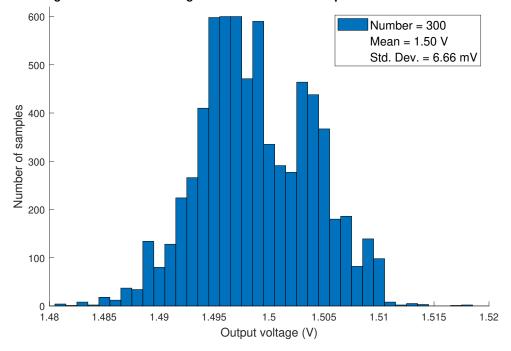

| 3.6  | Histogram and its corresponding probability distribution for the output voltage in the offset Monte Carlo testbench, with $I_{\text{bias}}$ equal to 50 nA. The output contains the common-mode value $V_{\text{bot}} = 1.5 \text{ V}$ and the offset, which is represented by the standard deviation value $\sigma = 6.66 \text{ mV}$ .                                                                                                                                                                                                                                                                                                                                          | 33 |

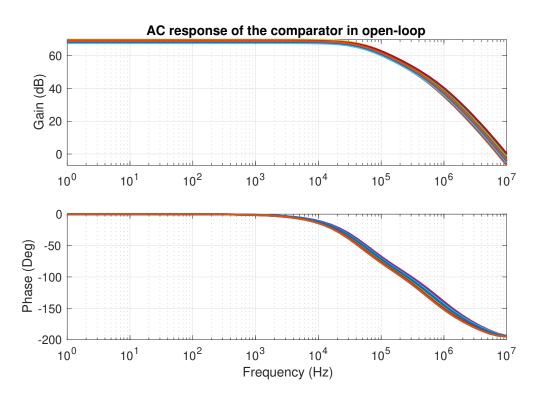

| 3.7  | Magnitude and phase in a corner AC analysis of the open-loop comparator, without the reset feedback. For nominal values the DC gain is 66.78 dB and the pole is located at 47.11 kHz. We define the process corners at -40 °C and 85 °C for fast-fast (FF), slow-slow (SS), fast-slow (FS), and slow-fast (SF) transistor models                                                                                                                                                                                                                                                                                                                                                  | 34 |

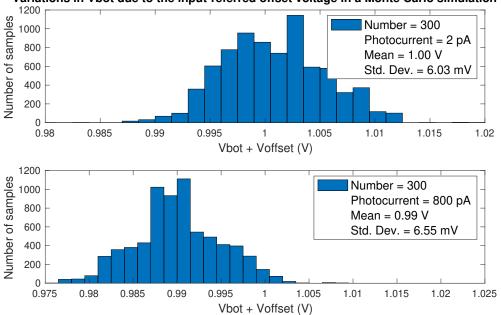

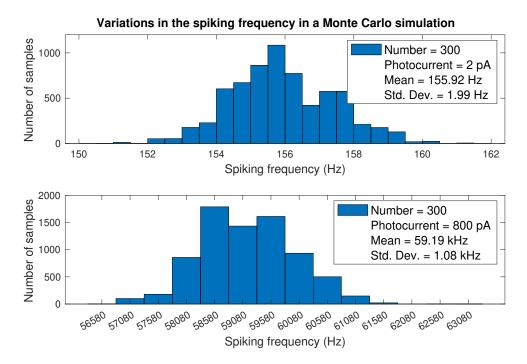

| 3.8  | Histogram of $V_{\text{bot}}$ with two different photocurrents in a Monte Carlo simulation.<br>The variations are the effect of mismatch. The displacement to the left is produced<br>at high frequencies. The comparison point is set at 1 V                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35 |

| 3.9  | Histogram of the spiking frequency of a pixel with two different photocurrents in a Monte Carlo simulation. Same conditions as above                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36 |

| 3.10 | (Left) Original test image in greyscale. (Right) Test image after adding random frequency variations with the achieved standard deviation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36 |

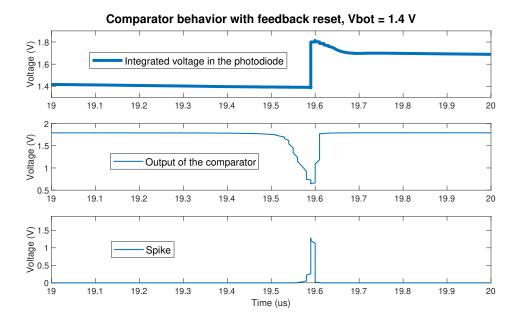

| 3.11 | Transient simulation characterizing the behavior of the comparator. The fall time is 60 ns and the rise time is 15 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37 |

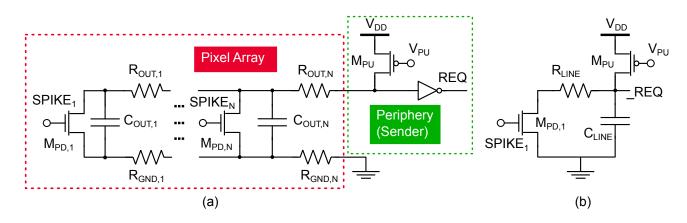

| 3.12 | (a) Wired-NOR circuit implemented in the pixels' rows and columns, and the sender<br>block in the periphery (the circuits in the sender are explained later). $C_{out}$ and<br>$R_{out}$ represent the drain capacitance, the line crosstalk, the output resistance and<br>the line resistance, respectively. (b) Equivalent circuit of the wired-NOR, neglect-<br>ing the influence of $r_o$ and $R_{GND}$ . $M_{PD}=2/0.18$ , $M_{PU}=18/0.7$ , $R_{line}=235.6 \Omega$ and                                                                                                                                                                                              |                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|      | $C_{line} = 600.1  \mathrm{fF}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38              |

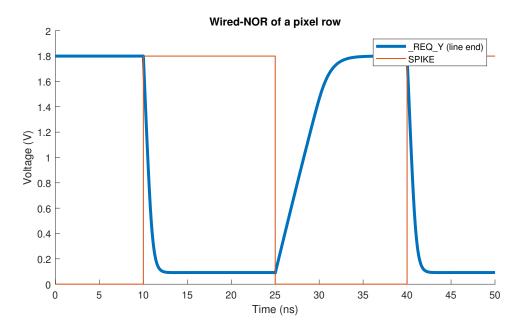

| 3.13 | Transient simulation of the circuit in Fig. 3.12(b), implementing a wired-NOR in a row of 95 pixels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39              |

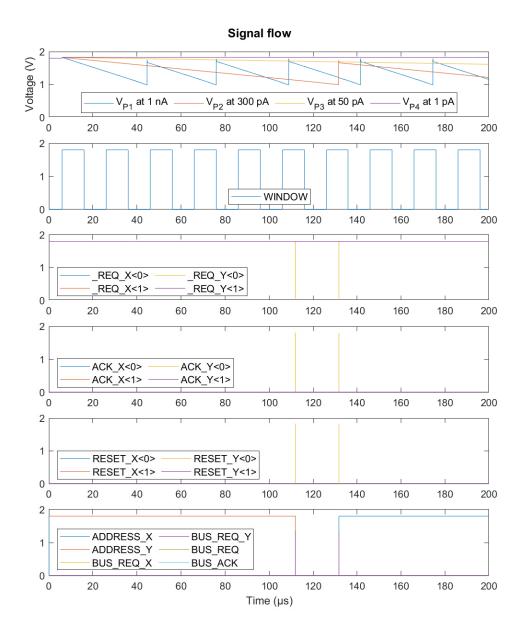

| 3.14 | Handshaking protocol in a transient simulation for a cluster of four pixels, with two transmitted spikes. First, the voltage $V_P$ in the input $C_{ph}$ capacitance decreases until it reaches the comparison value $V_{bot}$ . The output of the comparator resets $V_P$ to $V_{DD}$ . The spike at $t = 105 \mu s$ is transmitted if it occurs while WINDOW is high. The spike generates the _REQ_X<0>, which is answered by the row arbiters with a ACK_X<0> and RESET_X<0>. Then, _REQ_Y<0> produces BUS_REQ and RESET_Y<0>; the sensor (AER transmitter) sends its address to a external processor (AER receiver), while the spike stored in the pixel is terminated | 40              |

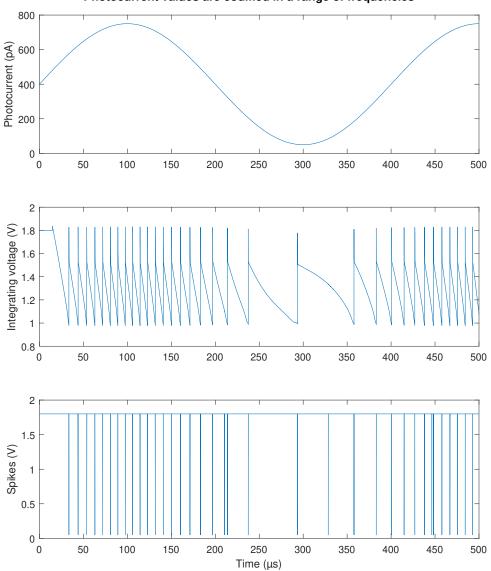

| 3.15 | Transient simulation with a sinusoidal input photocurrent being codified in spikes at different frequencies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41              |

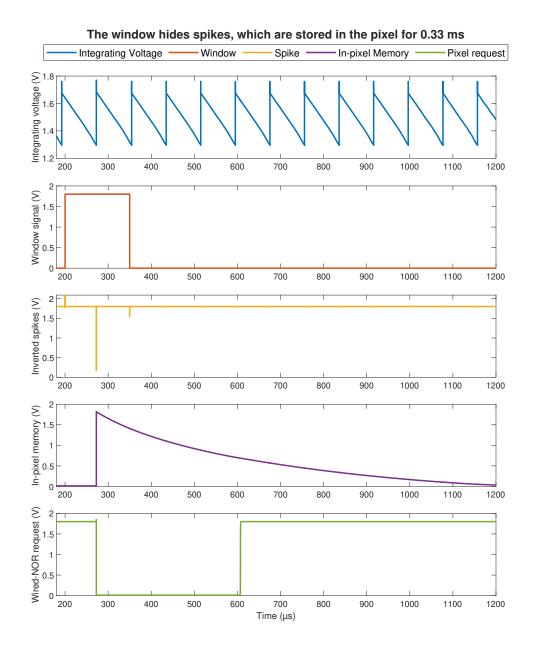

| 3.16 | Transient simulation to represent the window masking capability, in conjunction with its in-pixel memory. Events are stored for 334.44 µs before they are discarded due to current leakage. Spikes and requests use active-low logic in the in-pixel handshake protocol.                                                                                                                                                                                                                                                                                                                                                                                                   | 42              |

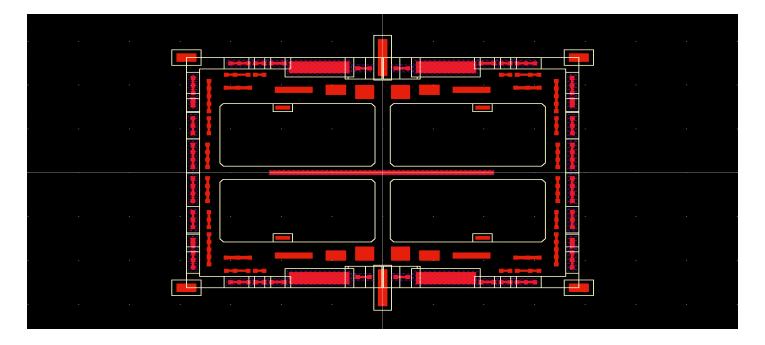

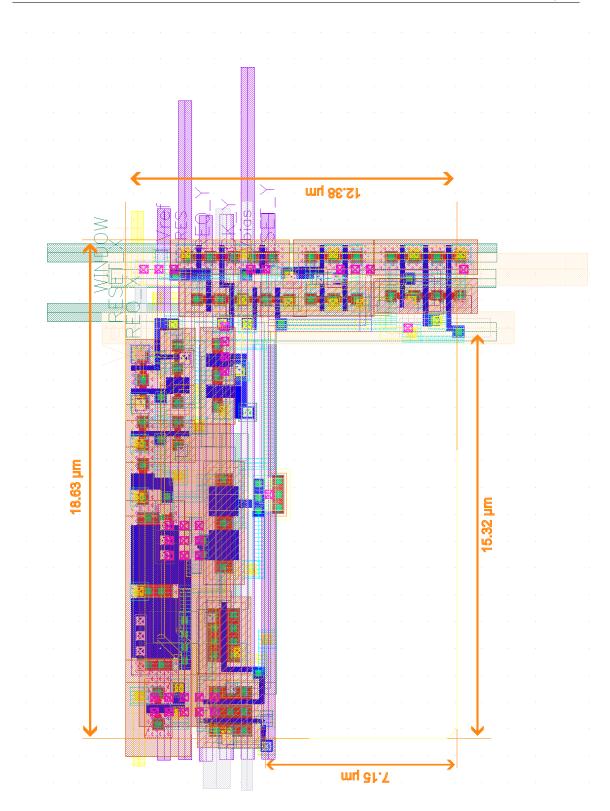

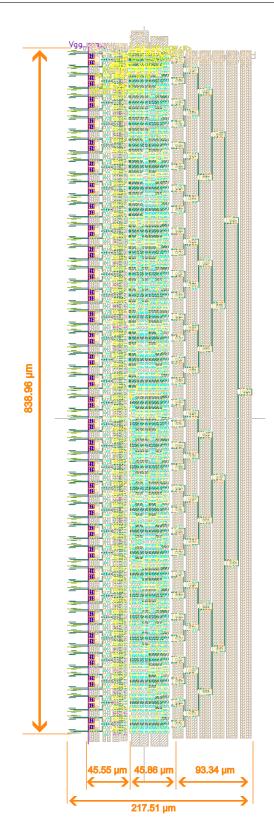

| 3.17 | Layout of a pixel cluster, showing the NWELL, PPLUS and active layers. Pixels<br>in the cluster share the NWELL, as well as with their neighbors. PWELL is con-<br>nected to ground in every cluster. By seeing the active areas we can interpret the                                                                                                                                                                                                                                                                                                                                                                                                                      | 42              |

| 3.18 | arrangement of the transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43              |

| 3.19 | that cross the pixel matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44              |

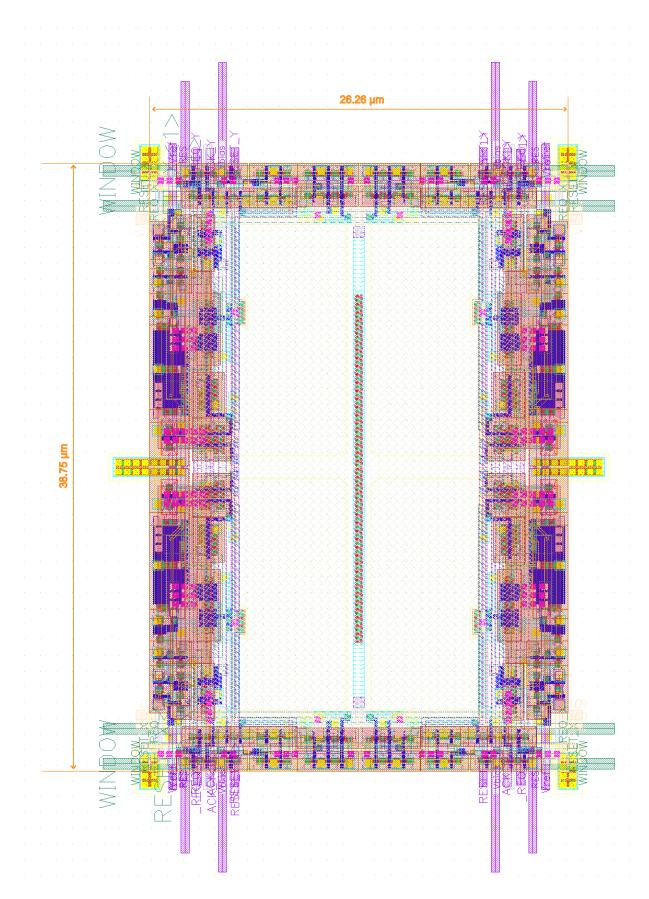

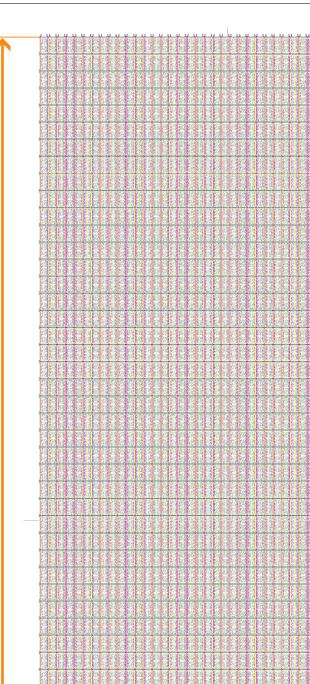

| 3.20 | fulfillment of design rule checks (DRC) and achieve a more compact arrangement.<br>Layout of the pixel matrix with a 96 x 64 resolution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\frac{45}{46}$ |

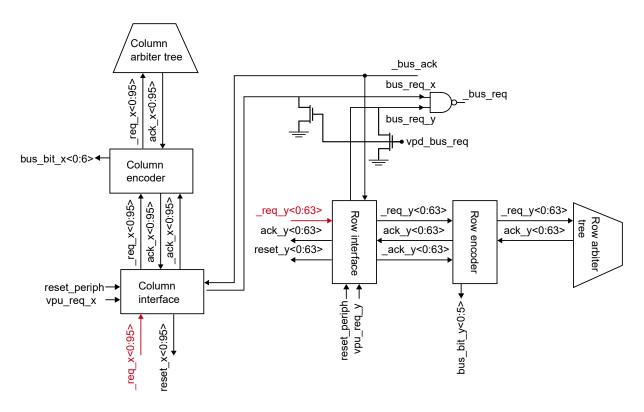

| 4.1  | Block diagram of the AER periphery and its signals. The wired-NORs are marked<br>in red. The pixel matrix sends a request in both dimensions and receives a row<br>acknowledgment (there is no need for column acknowledgment) and a reset in both<br>dimensions. The pixel matrix is omitted for brevity.                                                                                                                                                                                                                                                                                                                                                                 | 47              |

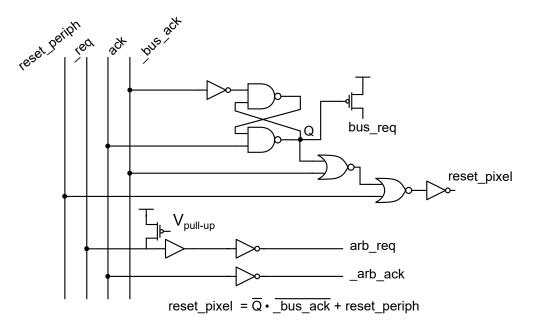

| 4.2  | Schematic of the sender. It implements the buffering of the wired-NOR signal, which<br>goes directly to the arbiter tree. An acknowledge arrives and is latched, triggering<br>a chip request in the AER bus for its corresponding dimension. The acknowledge<br>is also inverted to activate certain bits of the encoder. When the aknowledge from<br>the AER sender is received, the pixel is reset. Notice that all signals are related to                                                                                                                                                                                                                              |                 |

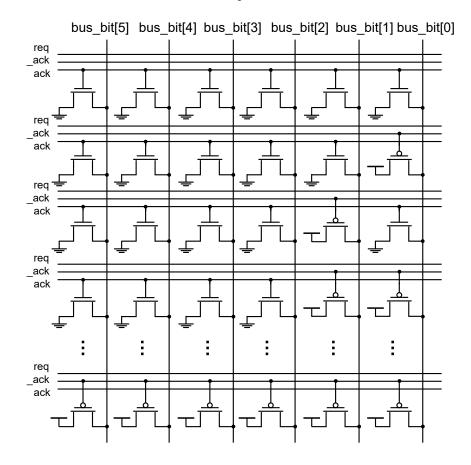

| 4.3  | their dimension, since there is a sender for rows and columns. $\dots \dots \dots$<br>Schematic of the row encoder. All transistors have minimum length and $W = 3 \mu m$ .<br>The request line crosses the block without connections to reach the arbiter tree.<br>The output is an N bit signal to encode $2^N$ addresses. There is another encoder for                                                                                                                                                                                                                                                                                                                  | 48              |

| 4.4  | columns with one more bit. Each encoder has an output bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49              |

|      | which is not an exponential number with base 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50              |

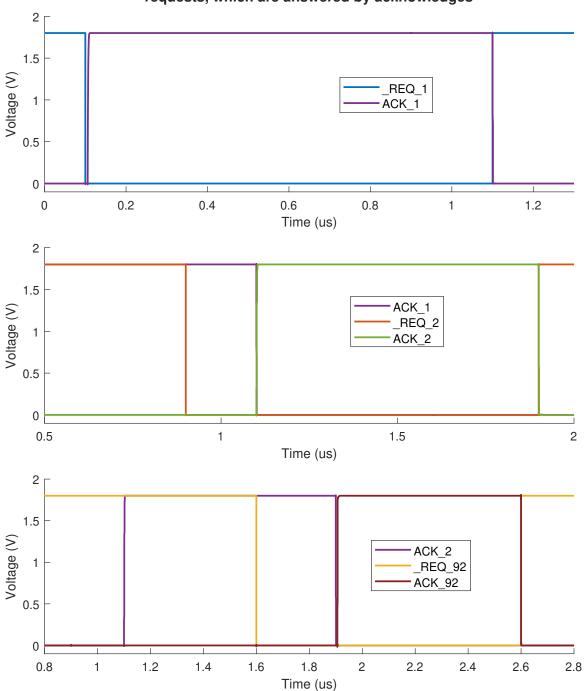

- 4.5 Post-layout verification of the AER blocks. The column circuits (sender, encoder, and arbitration tree) are tested with three requests coming from neighbor and extreme pixels. ACK1 comes 6.45 ns after REQ1 goes high, ACK2 comes 0.98 ns after REQ1 goes low (with REQ2 active), and ACK3 comes 6.63 ns after REQ2 goes low (with REQ3 active).

# List of Tables

| 2.1 | Comparison Between Asynchronous and Synchronous Readout Techniques in Dy- |    |

|-----|---------------------------------------------------------------------------|----|

|     | namic Vision Sensors in Works Reported in the Liturature                  | 13 |

| 2.2 | Temporal Characteristics of our Octopus Sensor                            | 21 |

| 5.1 | Comparison to Other Octopus Sensors reported in the Literature            | 55 |

### Abstract, Motivation and Objectives

#### Abstract

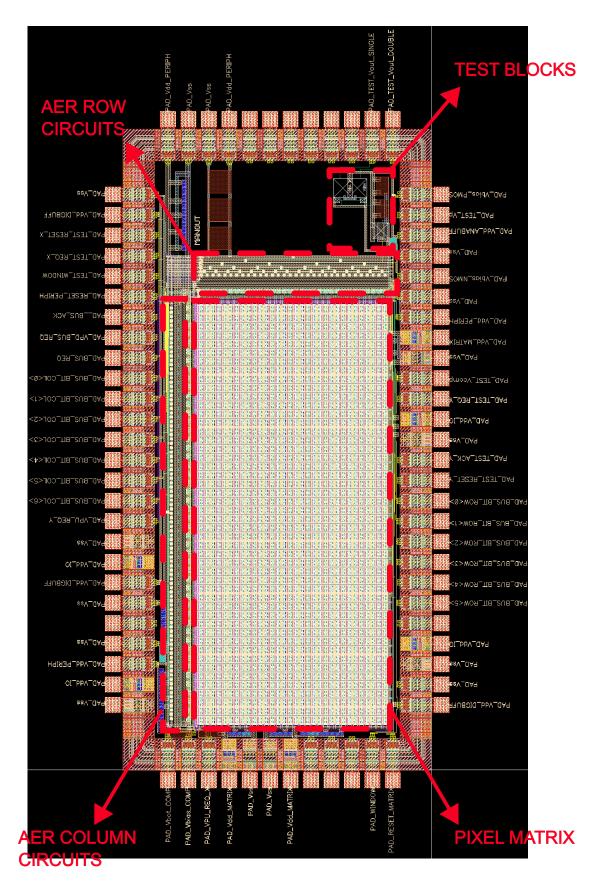

This Master's Thesis focuses on the design of an octopus image sensor using UMC0.18 technology. We incorporated a logic for decoupling spike generation from readout, aiming to solve the main issues that affect octopus architectures. This type of event-based sensor encodes the intensity of the light hitting each pixel in a frequency of pulses, known as events or spikes. Spikes are subsequently read out using asynchronous logic involving wired-NORs, arbiters, and encoders. The operation of the imager is divided into three main parts: (1) integration of light and conversion into a one-bit pixel request signal, (2) row and column arbitration to select the output pixel, and (3) encoding of the pixel address, acknowledgment, and reset.

Chapter 1 provides an overview of the development of event-based imagers and compares them with mainstream digital image sensors such as CCD or CIS APS. The unique characteristics of event-based image sensors are presented, with a specific focus on the octopus sensor and the AER asynchronous readout protocol.

In Chapter 2, the limitations of the asynchronous readout scheme are discussed in greater detail compared to conventional synchronous readout. Various types of arbiters used in asynchronous systems are explained. The final section of Chapter 2 encloses the theoretical framework supporting the implementation of the decoupling logic and motivating the integration of the chip described in this work. The two readout modes to be tested in the laboratory in future research, namely the sparse readout mode and the quanta image mode, are presented.

Chapter 3 delves into the design details of the pixel, providing an explanation of its operation and a step-by-step guide to designing the comparator, which is the most sensible component within the octopus pixel. The functioning of the in-pixel handshake interface is highlighted, and layout and post-layout verifications are performed.

Chapter 4 revisits the AER circuits discussed in the previous chapters, showcasing their implementation in the designed sensor along with the layout and post-layout results.

Finally, Chapter 5 describes the results we expect to obtain in the laboratory and the potential of spike decoupling in asynchronous readout for all classes of event-based vision systems.

#### Motivation and Objectives

A well-known feature of octopus sensors is that brighter pixels receive more attention in asynchronous readout. Because the integration threshold is reached faster in brighter pixels, they request bus access more frequently. This can lead to motion artifacts in the image, as a bunch of pixels hoards the whole bus bandwidth for themselves. Traditional synchronous readout schemes allocate an equal portion of the bandwidth to all pixels regardless of their activity, effectively preventing such congestion. The limited bandwidth of the arbiters in the asynchronous periphery has hindered the application of octopus sensors to specific tasks, such as tracking small and intensely luminous light sources.

In this work, we propose a simple solution using an asynchronous windowed readout scheme to alleviate congestion in the AER channel, reducing the bias toward brighter pixels in favor of darker ones. Our solution is based in the assumption that it is more advantageous to have spatially sparse information, meaning that it is preferable to have more pixels firing, even if each pixel fires less frequently. By decoupling event generation from readout and leveraging the in-pixel aging storage mechanism, we anticipate being able to capture spike data from a larger number of pixels in high-illuminance scenarios, regardless of any spikes that may be missed from more active pixels.

Also, the sensor we designed aims to test the hypothesis that by employing observation windows to capture spikes, we can effectively preserve the most relevant aspects of the image by leveraging the Poisson distribution of the spiking matrix output. This method is inspired by the quanta image sensor (QIS). While QIS relies on single photon detection and justifies its usage of Poisson arrival statistics based on the random nature of photon arrivals, we seek to experimentally verify whether we can replicate a similar readout scheme in the laboratory by constructing binary bit planes using the spikes from our octopus pixels.

The result of this work is a design that was send for manufacturing, and that will allow us to specifically investigate these approaches in an octopus sensor. The testing of the fabricated sensor and of the proposed readout schemes is beyond the scopes of this work. Although this is the only class of event-based sensor that performs light-to-frequency conversion, we expect that future studies on our sensor can have an impact on related aspects of other event-based sensors, such as motion artifacts, scalability, and data compression. To achieve this result, this work have dealt with the following tasks:

- The successful design and development of an octopus image sensor in UMC0.18. The design process required careful consideration to ensure its viability for manufacturing and future studying and dissemination of results.

- The primary purpose of this sensor is to serve as an experimental platform for validating the proposed readout schemes. Future laboratory experiments will evaluate the extent of data reduction achievable through the decoupling technique and examine the trade-offs between data reduction and image quality.

- A thorough examination of the evolution and current state-of-the-art in readout schemes employed in event-based imagers was conducted, both synchronous and asynchronous. This involved studying existing techniques and understanding their strengths and limitations.

- Establishing a clear and well-justified theoretical framework for the future implementation of the asynchronous windowed readout was an essential aspect of this work. The framework provides the necessary guidelines and principles for designing and implementing the decoupling logic and exploring its potential benefits in the future.

### CHAPTER 1

### Fundamentals of Octopus Image Sensors

#### **1.1 Introduction**

The oldest surviving photograph was taken in 1826 [1]. To capture it, French inventor Nicéphore Niépce used a camera obscura containing a metal plate coated with a light-sensitive bitumen and faced it out of a window in his estate in Le Gras. Due to the low light sensitivity of the material, Niépce exposed the sensor for a few days in broad sunlight. He then dipped the plate in a diluted lavender oil bath to develop the latent image, dissolving the less-exposed bitumen parts and thus resulting in a negative image. What Niépce had conceived is a chemical process that we now call contact print, the basis of film photography. Despite its lack of visual appeal, the image stands as a testament to the early crafts of image-sensing techniques, a concept that would eventually evolve into the sophisticated image-capture technologies we enjoy today.

Modern photography is intrinsically associated with digital cameras. A digital image sensor is fabricated on a piece of semiconductor, which alter its electronic properties when struck with photons of a specific energy. From here, we can measure the intensity of the light by measuring the current or the voltage induced in the semiconductor. In 1969, AT&T Bell Labs engineers Willard Boyle and George Smith developed the charge-coupled device (CCD), leading to the first digital image sensor to take off to the mass market [2]. CCD image sensors originally used MOS capacitors to accumulate the photo-generated charge in silicon, which were unaffected by the manufacturing issues that troubled early passive and active pixel sensors. The packets of charge in a line of MOS capacitors were then shifted to the next line, until reaching a fast shift register for amplification and readout. This architecture was improved in 1980 with the pinned photodiode (PPD), that solved its inherent shutter lag. Due to their invention, Boyle and Smith won the 2009 Nobel Prize in Physics, along with Michael Tompsett [3].

CCDs had a long list of drawbacks that seem unsolvable. The thousands of charge transfer steps required to readout each pixel consumed considerable energy, making them hard to scale to larger pixel counts. Also, they required external processing components outside the chip, which made them bulky, heavy, and power-hungry; and suffered from undesired effects such as smearing or blooming. These constraints paved the way in 1992 for Eric Fossum to develop the active pixel sensor (APS) or CMOS image sensor (CIS) [4]. While he was working for the NASA Jet Propulsion Laboratory at Caltech, he figured out an architecture that had in-pixel charge transfer and amplification, so NASA could embed lower-powered and more compact image systems in their missions. Also, CMOS sensors could be manufactured in standard CMOS fabrication processes, which made production a lot easier and more affordable than CCDs.

Figure 1.1: Comparison between CCD and CMOS image sensors [5]. (a) CCDs transfer simultaneously the signal charges of its photoreceptor, as received, to the next CCD. A fast shift register at the end of the lines sends them to an amplifier for external readout. (b) A CIS uses amplification in each pixel, converting the signal charge into a voltage signal . Although CIS were more sensible to fixed-pattern noise (FPN), this drawback has been eliminated.

Designers could integrate all the timing, control, and signal-processing CMOS circuits on the same CIS. Fossum founded the spinoff company Photobit in 1995 to develop and commercialize the CMOS APS. Only six years later, Photobit was acquired by Micron. During those days, Micron became the world's largest supplier of image sensors [6]. As of 2023, those charts are led by Sony and Samsung, but the industry is still largely dependent on IPs licensed by Caltech [7, 8]. It is estimated that over 6.5 billion CMOS APS were shipped worldwide in 2020.

As we have seen, mainstream image sensors consist of a photosensitive array that provides absolute illumination values at each point of an image, typically acquired frame-by-frame at a fixed sequential rate. These systems differ greatly from biological systems found in most animals, where cells operate independently and asynchronously, primarily focused on reporting changes. In an attempt to mimic the behavior of biological systems, the development of neuromorphic silicon retinas or event-based image sensors has run parallel to the development of CIS [9]. These endeavors languished in front of CIS chips for three decades. However, event-based sensors are now gaining industrial traction due to their high temporal resolution, very high dynamic range, low power consumption, and high pixel bandwidth [10]. The arrival of industrial giants in this field is bringing new methods and techniques for event-based sensing, with promising applications in machine vision and related AI tasks in which image quality is not essential.

#### **1.2** Event-based image sensors

"These guys are saying that a nerve membrane works like a transistor. Is this right? —Delbruck asked Mead brusquely" [11]. It is 1967, and Carver Mead is a teacher at the California Institute of Technology (Caltech), in Pasadena. Mead has a growing reputation as a world-beating expert on transistor physics. He was an advisor and collaborator of Gordon Moore while working at Fairchild Semiconductor, who credits him for coining the term Moore's Law [12]. Max Delbruck,

Figure 1.2: Historical evolution of digital image sensors. Originally from [5], modified in this work.

a biophysicist also working at Caltech on bacteria and their viruses, earned the 1969 Nobel Prize in Physiology or Medicine. After that initial meeting, Mead would dedicate his research efforts to neuromorphic engineering: a field for analog, digital, and mixed-signal VLSI implementation of neural systems models. Mead's group at Caltech gathered the most relevant names in the field, with the likes of Misha Mahowald, who implemented the first silicon VLSI retina; Tobi Delbruck, son of Max and developer of the dynamic vision sensor (DVS) [13]; or Kwabena Boahen, who formalized the address event representation (AER) communication channels between neuromorphic chips [14]. They were strongly influenced by the works of Fukusima and its neocognitron. To this day, the greatest success of neuromorphic systems has been the emulation of vision signal acquisition and transduction, resulting in a family of event-based image sensors.

Neurons play a fundamental role in the brain by receiving sensory information, processing it, and transmitting the results to other neurons, ultimately influencing bodily functions and movement. Neuronal communication occurs through action potentials, also known as spikes, which are sudden changes in a neuron's membrane potential. These spikes have a fixed shape and amplitude and can be chemically transmitted to other neurons. Simplified models of neurons suggest that spikes are generated when the integration of electrical current input exceeds a certain threshold. This

Figure 1.3: Silicon retina designed by Mahowald [16]. (a) Diagram of the silicon retina showing the resistive network and a single pixel element. (b) Address event representation (AER) scheme. Asynchronous neurons request control of the bus when they generate action potentials and transmit their addresses.

process, often referred as the integrate-and-fire neuron model, can be compared to a tipping bucket, where the neuron collects and integrates input current until it reaches a threshold, at which point a spike is emitted. Consequently, the neuron's output is encoded in the timing of these spikes, creating a stream of spikes with a constant amplitude that is transmitted to other neurons.

Event-based image sensors, or event-driven image sensors, work by compressing light intensity values within their pixels. Unlike mainstream image sensors, these pixels do not transmit analog or digital absolute light intensity information. Instead, they perform all the necessary analog processing at the pixel level and transmit an action potential called an event or spike. As a result, an event-based pixel matrix produces a set of spikes, or events, based on the pixel architecture. Although we can think of the spike as a 1-bit digital signal, it behaves more like an impulse that carries the time at which the event occurred. The sensor typically encodes the timestamp of the spike either on-chip or externally while transmitting the address of the firing pixel. Consequently, event-based sensors are intrinsically asynchronous, with each pixel autonomously detecting and transmitting events. This event-driven operation frees the sensor from a fixed time-step, allowing it to remain idle until a spike occurs, naturally responding to the visual scene. Efficient spike encoding ensures that the number of updates is minimized.

We can distinguish several classes of event-based sensors depending on how events are produced [15]. The original works published by Mahowald and her colleagues implemented spatial contrast detection by computing the average illumination values between neighboring pixels through a diffusive network of MOS variable resistors and comparing it with local pixels [16]. If they differ, the pixel spikes. Mahowald already implemented the AER protocol in its silicon retina.

Mahowald's design was later improved by Zaghloul and Boahen [9], with additional features modeled after layers of the biological retina. But these silicon retinas had pixels that were vastly too big and noisy. Circuit complexity, silicon area, fill factors, noise levels, mismatch: they all languished in front of its CIS rival. The neuromorphic community used these first chips to demonstrate neurobiological models and theories, but did not find traction in real-world applications.

Eventually, the class of event-based sensor that stood out was the DVS. This family of sensors are only sensitive to temporal contrast, achieving extremely high temporal resolution (in the order

Figure 1.4: Preliminary image deblurring results on high-speed scene, obtained combining Prophesee Metavision sensor and algorithms with Snapdragon platform.

of µs), intrascene dynamic range (up to 140 dB) and low latency (also µs). More importantly, these sensors squeeze a lot of information about the visual scene without the need of external processors, optimizing data transfer, storage, and processing, hence increasing power efficiency and compactness of the vision system. It is a prime example of sparse computing: the removal of use-less and redundant data, computing only where and when needed. The foundational paradigm of neuromorphic engineering. Besides, by shifting performance constraints from the voltage domain into the time domain, dynamic range is no longer limited by the power-supply rails, thus providing relative immunity to the aggressive supply voltage scaling of modern CMOS technologies. Nowa-days, DVS are find frequent applications in robotics, tactile sensing, high-speed control, driving, space and computational photography.

Delbruck and Patrick Lichtsteiner came up with the DVS while working on the European project CAVIAR [17]. Their pixel design had three main blocks: an active unity-gain logarithmic photoreceptor, which is buffered to a capacitive-feedback amplifier that computes the temporal derivative of the voltage induced by the photoreceptor, and a couple of comparators that monitor the amplified voltage. This pixel produces ON and OFF events, depending on whether there is a positive or negative temporal contrast. These sensors have received considerable attention by the industry, to the point where they have become synonymous with event sensors, and are well suited for high-speed motion detection and analysis, object tracking, and shape recognition, among many others [10].

DVS cameras are already available on the shelves. Actually, some companies already have several generations in their line of products. Sony's IMX636ES was designed in collaboration with Prophesee, a French company with four sensors in their catalogue. Then there is iniVation, a spin-off of the ETH Zurich participated by Delbruck, with three manufactured sensors. Samsung also has three, whereas the Chinese start-up has launched two. All of them have published their results in different editions of the ISSCC [18, 19, 20, 21, 22, 23, 24].

Delbruck's pixel architecture served as the foundation for subsequent generations of DVS developed by the major players, which have been incorporating new features into their designs. Delbruck itself reported the DAVIS in 2014 [25], a hybrid sensor that combines the DVS and APS. The DAVIS enabled both conventional frame-based sampling of intensity and asynchronous detection of logarithmic intensity changes. Besides, a significant breakthrough seems to be underway, as Prophesee garnered considerable attention at the 2023 Edition of the Mobile World Congress. Event-based sensors have emerged as a viable option to complement frame-based methods, particularly in consumer-facing products. In light of this, Prophesee has partnered with Qualcomm to enhance the quality of smartphone cameras in fast-moving dynamic scenes. It won't be long before we start seeing these products integrated into wearables or AR/VR headsets.

However, recent literature indicates a shift in the principles of these sensors. There is a growing trend among companies towards synchronous readout schemes, deviating from the traditional asynchronous arbitration of spikes using wired-NOR circuits. The limitations of large sensor formats and the unpredictable arbitration time of asynchronous systems have led companies to favor more deterministic approaches. Although Prophesee and Sony previously utilized a mix of asynchronous arbitration between pixel rows and sequential scanning of columns, their most recent research reveals a shift towards event-based vision sensing combined with conventional framed image acquisition.

A seemingly inevitable drawback of event-based sensors is their lower spatial resolution when compared to CIS imagers: pixel count is usually below 1 MP. Besides the limits imposed by current asynchronous handshake circuits, the complexity of the pixels' circuitry is a constraint for reduced pixel pitch. Traditionally, pixel sizes have ranged from 17 µm to 50 µm, although new designs have achieved sizes as small as 4.95 µm through vertical integration [26]. In this work, we address the issue of scalability in event-based sensors. Before delving into the limits of the AER readout scheme, let's provide more details about the specific class of event-based sensors implemented in our work.

#### 1.2.1 Octopus sensor

We have already discussed two classes of event-based sensors: those that encode spatial contrast in their events and those that are sensitive only to temporal contrast. A third class consists of bioinspired image sensors that transmit pixel absolute intensity in the timing of events. While many of these sensors do not achieve redundancy suppression or latency reduction, they do benefit from other properties of event-based sensing, such as high dynamic range, low-power operation, and high SNR. Pulse-modulated (PM) imagers, with various architectures, usually employ a comparator as a fundamental building block [27], and benefit from smaller pixel size compared to other event-based sensors. Unlike conventional CIS imagers, which integrate photocurrent for a specific scanning period and then read the integrated voltage in a raster scan, PM image sensors integrate photocurrent until it reaches a fixed voltage threshold, autonomously generating a spike when crossed.

One implementation of time-domain encoding is the time-to-first spike (TTFS) image sensor, which uses pulse-width modulation (PWM) schemes by measuring the time between a pixel's reset and the switching of the comparator. Time is measured using pixel-level or global timers. A measurement cycle starts when the photodiode voltage is reset to a defined voltage level, which is then discharged by the photo-generated current. A comparator continuously compares the integration voltage ramp to a voltage reference. The incident light intensity is inversely proportional to the integration time. Then again, the measurement is not externally governed as in a conventional APS or CCD, and each pixel is allowed to autonomously choose its own optimal integration time. Once the threshold is reached, a pulse is generated.

In 2011, Christoph Posch introduced the asynchronous time-based image sensor (ATIS) [28], which combined a DVS architecture for change detection with absolute exposure measurement carried out locally by individual pixels using a TTFS circuit triggered by change detection. The

Figure 1.5: Pulse-modulation imagers [28] These pixels transmit absolute intensity of incident light through the timing of events in the comparator's output. (a) Time-to-first spike (TTFS) architecture, based on PWM. Brighter pixels spike sooner than darker pixels. (b) Octopus pixel architecture, using PFM encoding. Larger photocurrents are converted into higher frequencies.

authors reported an intra-scene dynamic range of 143 dB static, 125 dB at 30 fps equivalent temporal resolution, a typical SNR of 56 dB, and a FPN under 0.25%. The sensor was fabricated on UMC180, with a supply voltage of 3.3 V and 1.8 V for analog and digital circuits, achieving QVGA resolution with a pixel pitch of 30 µm x 30 µm and a fill factor of 30%. They implemented asynchronous readout through an AER channel. The pixels comprised 77 transistors, 3 capacitors, and 2 photodiodes, and power consumption of the entire sensor was 175 mW.

In this work, we implement the octopus sensor, which utilizes pulse-frequency modulation (PFM). Octopus pixels encode their absolute light intensity in the frequency of spikes emitted by each of them. Their implementation is similar to that of TTFS imagers, but with a self-reset mechanism in the voltage ramp, initiating a new integration cycle each time the voltage threshold is reached. The interspike interval is inversely proportional to the incident light's photocurrent, so that a higher event rate corresponds to a brighter pixel. Octopus pixels can achieve spiking frequencies of dozens of kHz. However, the precision of frequency measurement is limited by the voltage offset of the comparator induced by mismatch, which can lead to FPN, as well as by kTC noise, by charge injection in the reset transistor, and by the switching delay of the comparator.

Culurciello and Boahen introduced the first octopus sensor in 2003 [29]. They described a current-feedback event generator for monitoring the integrated voltage and generating spikes upon reaching the threshold. The architecture aimed to minimize power consumption while maximizing gain and bandwidth. Readout was asynchronous using the AER protocol with wired-ORs for arbitration. The matrix resolution was 80 x 60, with a pitch of  $32 \,\mu\text{m} \times 30 \,\mu\text{m}$ , and a fill factor of 14%. They achieved a dynamic range of 120 dB and a maximum bandwidth of 40 MHz for the entire array, with a maximum update rate per pixel of 8300.

One notable feature of octopus sensors, as observed by the authors, is that brighter pixels receive more attention in asynchronous readout. Because the integration threshold is reached

Figure 1.6: Schematics and images from the original octopus sensor [29]. (a) Asynchronous AER readout. A latch buffers the request from the pixel. The request signals are arbitred in the arbitrer trees, which select the first pixel that produced an event. The encoders output the address of that selected pixel. (b) Pixel schematic, showing the current-feedback event generator and the in-pixel handshake circuit. (c) Example images with linear intensity (top) and log scale (bottom).

faster in brighter pixels, they request bus access more frequently. This can lead to motion artifacts in the image, as a bunch of pixels hoards the whole bus bandwidth for themselves. Traditional synchronous readout schemes allocate an equal portion of the bandwidth to all pixels regardless of their activity, effectively preventing such congestion. The limited bandwidth of the arbiters in the periphery has hindered the application of octopus sensors to specific tasks, such as tracking small and intensely luminous light sources. In this work, we propose a simple solution using an asynchronous windowed readout scheme to alleviate congestion in the AER channel, reducing the bias toward brighter pixels in favor of darker ones.

Octopus sensors have demonstrated usefulness in tracking small and bright light sources [15]. Their excellent temporal resolution, low power consumption, and reduced data output make them suitable for space navigation, precisely gauging the sun's position. [30]. These digital sun sensors have evolved into more compact and efficient solutions, incorporating TTFS operation [31] or utilizing photodiodes in the photovoltaic region for self-powering [32]. Octopus sensors have also been proposed for flame monitoring using NIR filters [33] and color detection [34]. Additionally, in the early 2000s, they were considered for retinal prosthesis applications [35].

While readout saturation and large FPN have limited their use in conventional imaging applications, efforts have been made to address these drawbacks. For example, authors in [36] incorporated in-pixel spike counting and memory in 8-bit Gray code format for parallel counting and readout. Their synchronous architecture allowed them to capture snapshots of the scene during the integration period. Leñero integrated several hybrid pixels with pulse-frequency modulation and contrast computation [37], APS [38], and frame-based readout [39]. Recently, a method involving synchronous readout of spikes in octopus image sensors was proposed [40].

#### 1.2.2 Address event representation (AER)

Event-based image sensors draw inspiration from the computational processes of biological systems, but some of these can not be translated into silicon in a feasible way. While our brains are composed of a highly-dense 3D network of neurons, axons, and synapses, CMOS technology is fundamentally 2D and cannot replicate such intricate wiring. In a neural network, a single neuron is typically interconnected with thousands of other components, whereas standard digital logic gates typically connect to only a few inputs. This physical disparity presents a constraint for artificial vision systems, where each pixel would require a dedicated wire to convey its data out of the array. However, designers overcome this limitation by capitalizing on the remarkable speed of transistors. Unlike the spiking activity of a neuron, which lasts for milliseconds, the switching delay of a transistor is on the order of picoseconds. Taking advantage of this discrepancy in timescales, communication in neuromorphic systems is often implemented using a time-multiplexed, packetswitched communication method called address event representation (AER).

A packet-switch network operates by time-multiplexing individual segments of the network, with packets being communicated requesting access to shared resources on the fly. Such protocols suit networks where two endpoints exchange bursts of small amounts of information, such as spikes in a neuromorphic system. AER provides the multiplexing and demultiplexing functionality for the spikes that are generated by or delivered to a cluster of neurons. Notice that AER is also used to create networks of neuromorphic processors that can send and receive spikes, but in the context of event-based image sensing there is no need to communicate spikes to the pixels. In our application, a standard digital processor acts as the AER receiver, processing spikes as they arrive. Practically all bioinspired vision sensors with spiking output reported in the literature use the AER protocol, or some modified version, to communicate their data.

Given that spikes are generated asynchronously, the AER sender circuits in an event-based sensor must accept spikes as they are generated, arbitrate between simultaneous spiking pixels, encode the address of the first firing pixel, and multiplex the address in the shared bus. Additionally, a routing topology within the pixel matrix is required to transmit the spikes to the AER circuits. Several schemes exist for each of these blocks, but we will focus on those implemented in octopus sensors described in the literature. For more detailed information on arbitration schemes, routing topologies, and AER receivers, we recommend referring to [41].

The AER sender of our octopus sensor is constructed as a 2D matrix of address-event sender elements, or pixels. The address event is represented by the row and column of the spiking pixel in a word-serial addressing scheme. Encoding and arbitration are done at the row level first and at the column level later. When both dimensions are finished, the pixel's row and column addresses are transmitted through a shared digital bus in a bundled-data 4-phase handshake asynchronous transmission, using a request signal (REQ), an acknowledge (ACK), and the data buses required to encode its location. Addresses transmit their implicit timing information of the spike, timestamped on the sensor itself or in the AER receiver. These blocks are represented in Fig. 1.7.

The AER circuits in both dimensions are almost identical. The only difference is that the pixel does not need to receive the acknowledge column token. The first stage in the AER readout is a sender with four functions: buffering the request and acknowledge signals coming from and going to the pixel matrix, implementing the pull-up transistor of the wired-NOR routing topology, and controlling the logic for the AER multiplexing and pixel reset. There is a sender for each array

in the dimension, which is equal to the square root of the number of rows or columns,  $\sqrt{L}$ . The second stage is a tree-shape arbitration logic to solve contention and queuing, formed by  $\ln(\sqrt{L})$  number of stages. The third stage is the encoder, which is activated with the acknowledge signal. When both dimensions are arbitred, the sensor sends a request signal with inverted polarity to the AER receiver, which answers with an acknowledge to let know the sensor that it has access to the data bus. After that, the action potential of the spiking pixel is reset.

The scheme we described is the standard dubbed AER 0.02, used for single-sender to singlereceiver communications; that is, a point-to-point AER link. There are other schemes to implement the AER readout, with minor modifications in the arbitration block using ring arbitration [42], or radically different paradigms for the entire multiplexing sequence, such as the burst-mode operation [43]. The AER 0.02 standard was loosely defined, without specification of voltages, bus width, signal polarities, signal setup and hold times, or any kind of connector standard.

Figure 1.7: (a) Schematics of an octopus sensor as an AER sender implemented by Leñero [34]. The first stage provides buffering and signal control for requests and acknowledges pixel arbitration. Requests are sent to an arbiter tree, which selects the winning row or column through an acknowledge, which then selects a word from the encoder. (b) Signal flow of the arbitration between rows and columns, and the AER point-to-point link with a 4-phase handshaking protocol [38].

### CHAPTER 2

### Asynchronous Readout

This chapter describes the theoretical framework that is the basis for the research conducted in this work. Section 2.1 outlines the limitations of the asynchronous AER readout scheme in comparison to conventional synchronous readout methods. Section 2.2 delves into further detail regarding the various types of arbiters utilized in asynchronous systems, highlighting the reasons why fair arbiters fail to address the congestion issues in the readout channel. Finally, Section 2.3 introduces the technique proposed in this work, offering mathematical justification for its application and showcasing Matlab simulations to support its validity.

#### 2.1 Tenderness towards synchronous readout techniques

A neuromorphic system should outperform conventional technology. Historically, most neuromorphic applications have failed to convincingly demonstrate that the bioinspired approach is better than simply scaling logic and exploiting parallelism. Emulating the data-driven computation and communication architecture used in brains may not necessarily exceed the capabilities of the digital clocked paradigm. Vaguely stating that metronomic schedules are less resource-efficient than an event-driven approach do not guarantee superior performance in practical usage and adherence to constraints.

Designers at industry leaders such as Sony and Samsung have likely contemplated this issue. As discussed in Chapter 1, the industry has recently shown interest in event-based sensors, particularly to the DVS architecture. Initial implementations of DVS employed asynchronous AER logic for collision handling and event transmission. While subsequent designs, like the DAVIS sensor developed by Delbruck, integrated additional functionality such as global shutter with active pixel sensing (APS), the event reading still relied on asynchronous logic. These designs achieved event rates of up to 50 Meps and a pixel size of 18.5 µm.

In 2017, Samsung introduced a slightly modified approach in a VGA format DVS employing Grouped-AER (G-AER) [44]. Their scheme involved grouping 8 neighboring pixels within a column and treating them as a single entity. The ON and OFF events of the pixels within a group were processed in parallel. The readout scheme combined asynchronous handshake arbitration between columns with burst-mode clocked readout of rows for groups containing at least one firing pixel. Using a digital logic synthesized with a 50 MHz clock, they reported an event rate of 300 Meps, a pixel pitch of  $9 \,\mu$ m, and 50 mW of power consumption.

In 2018, the Swiss company iniVation implemented a low-resolution DVS with synchronous AER (SAER) [45]. They introduced an innovative and intricate readout scheme where the pixel matrix was controlled synchronously by external circuitry. The scheme utilized two distinct pulses:

one to capture an event frame into each pixel's internal event memory and another to reset the pixel. Pixels were organized into 2x2 groups that shared a digital logic responsible for reading their internal memory and determining whether to transmit their events. In this way, they performed pre-readout pixel-parallel suppression of noise and spatial redundancy. The readout process occurred sequentially in both dimensions, following a token-ring scheme where columns or rows that had spiked were read while those that did not were skipped. They reported an event rate of 180 Meps, a pixel pitch of 10 µm, and 4.9 mW of power consumption.

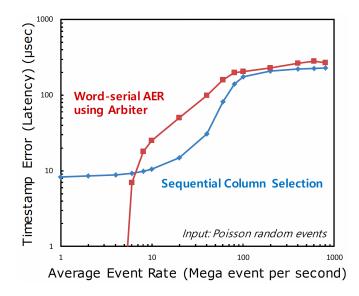

In 2020, Samsung made advancements in their DVS technology and scaled it up to a resolution of 1280x960 pixels [26]. The researchers acknowledged that higher resolution led to motion artifacts caused by timing errors within the limited bandwidth of event-driven readout. To address this, they took two approaches. First, they completely removed all asynchronous readout logic and replaced it with sequential column readout. The authors criticized the "unpredictable process timing inaccuracy" of the arbiter tree. Second, they introduced a global event-holding function using in-pixel storage cells, similar to the global shutter in CIS. This modification resulted in an event rate of 1.3 Geps, a pixel pitch of 4.95 µm, and 150 mW of power consumption.

Also in 2020, Sony collaborated with Prophesee to develop a 1280x720 DVS sensor that retained asynchronous arbitration in one dimension [22]. Rows were connected via a low-latency interface to an asynchronous selection tree. Events from the active row were promptly timestamped using an auxiliary time-out column located at the end of the pixel matrix. Subsequently, the entire row was scanned through an asynchronous-to-synchronous interface. The selection operation for the active row was pipelined, enabling parallel processing of previous data while new row arbitration took place. Additionally, their architecture was filled with on-chip digital processing of events. The reported specifications for this sensor were an event rate of 1.066 Geps, a pixel pitch of 4.86 µm, and 32 mW of power consumption.

In 2023, the ISSCC featured three papers describing modified DVS sensors with hybrid pixels in a stacked configuration, featuring significant architectural innovations. OmniVision presented a 1032x928 DVS matrix with a readout scheme similar to Sony's 2020 implementation [18]. However, the row-selection tree in OmniVision's design operated synchronously and was governed by a 250 MHz clock. The selected row was scanned entirely, and skip logic was implemented in both dimensions to bypass rows or columns that did not require reading. This sensor achieved an event rate of 4.6 Geps, a pixel pitch of 8.8 µm, and 46 mW of power consumption. The other two papers were designs by Sony [19, 20]. Both sensors followed the industry's trend of abandoning asynchronous readout in any form. In both cases, the output of the logarithmic amplifier was stored in a sample-and-hold circuit, which was then processed by a comparator using a three-phase logic. Events were read per row through a scan access mechanism, with a skip logic to ensure that only rows with at least one event were read.